.jpg)

CPLD (Thiết bị logic lập trình phức tạp) là gì?

Bài viết này sẽ hướng dẫn bạn về một thiết bị điện tử kỹ thuật số thiết yếu được gọi là CPLD (Thiết bị logic lập trình phức tạp).

Công nghệ thông tin, internet và chip điện tử đóng vai trò là nền tảng của thời đại kỹ thuật số hiện đại. Hầu như tất cả các công nghệ hiện đại đều bắt nguồn từ điện tử, từ internet và truyền thông di động đến máy tính và máy chủ. Điện tử là một lĩnh vực rộng lớn với nhiều nhánh nhỏ . Bài viết này sẽ giới thiệu cho bạn về một thiết bị điện tử kỹ thuật số thiết yếu được gọi là CPLD (Thiết bị logic lập trình phức tạp).

Sự phát triển của Điện tử Kỹ thuật số

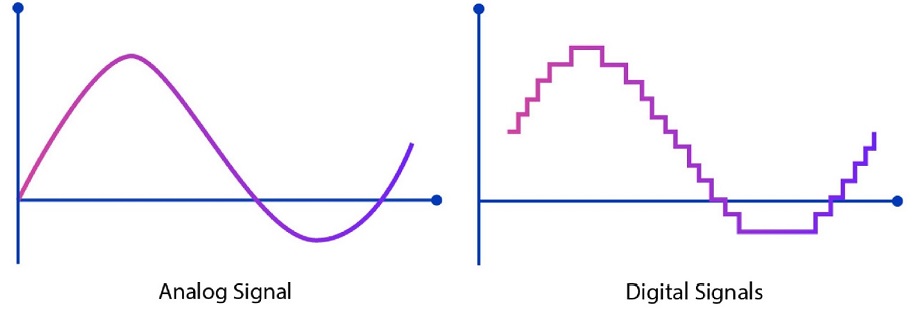

Điện tử là một lĩnh vực phức tạp với hàng ngàn thiết bị và linh kiện điện tử hiện hữu. Tuy nhiên, nhìn chung, thiết bị điện tử được chia thành hai loại chính: analog và kỹ thuật số .

Vào những ngày đầu của công nghệ điện tử, các mạch điện tử tương tự nhau, chẳng hạn như âm thanh, ánh sáng, điện áp và dòng điện. Tuy nhiên, các kỹ sư điện tử sớm nhận ra rằng thiết kế mạch tương tự rất phức tạp và tốn kém. Nhu cầu về hiệu suất nhanh chóng và thời gian xử lý nhanh đã dẫn đến sự phát triển của điện tử kỹ thuật số. Ngày nay, hầu hết mọi thiết bị điện toán đều tích hợp IC và bộ xử lý kỹ thuật số. Trong thế giới điện tử, các hệ thống kỹ thuật số hiện đã thay thế hoàn toàn điện tử tương tự nhờ chi phí thấp hơn, nhiễu thấp, tính toàn vẹn tín hiệu tốt hơn , hiệu suất vượt trội và độ phức tạp thấp hơn.

Không giống như vô số mức dữ liệu trong tín hiệu tương tự, tín hiệu số chỉ bao gồm hai mức logic (1 và 0).

Hình 1: Tín hiệu tương tự so với tín hiệu số

Các loại thiết bị điện tử kỹ thuật số

Các thiết bị điện tử kỹ thuật số ban đầu khá đơn giản và chỉ bao gồm một số ít cổng logic. Tuy nhiên, theo thời gian, độ phức tạp của mạch số ngày càng tăng, do đó khả năng lập trình đã trở thành một tính năng quan trọng của các thiết bị điều khiển số hiện đại. Hai loại thiết bị số khác nhau đã xuất hiện để cung cấp khả năng lập trình. Loại thứ nhất bao gồm thiết kế phần cứng cố định với phần mềm có thể lập trình lại. Ví dụ về các thiết bị như vậy bao gồm vi điều khiển và vi xử lý. Loại thứ hai bao gồm phần cứng có thể cấu hình lại để đạt được thiết kế mạch logic linh hoạt. Ví dụ về các thiết bị như vậy bao gồm FPGA, SPLD và CPLD.

Chip vi điều khiển có mạch logic số cố định, không thể sửa đổi. Tuy nhiên, khả năng lập trình đạt được bằng cách thay đổi phần mềm/phần sụn chạy trên chip vi điều khiển. Ngược lại, PLD (thiết bị logic lập trình) bao gồm nhiều ô logic có thể được cấu hình kết nối bằng HDL (ngôn ngữ mô tả phần cứng). Do đó, nhiều mạch logic có thể được thực hiện bằng PLD. Nhờ đó, hiệu suất và tốc độ của PLD thường vượt trội hơn so với vi điều khiển và vi xử lý. PLD cũng mang lại cho các nhà thiết kế mạch sự tự do và linh hoạt hơn.

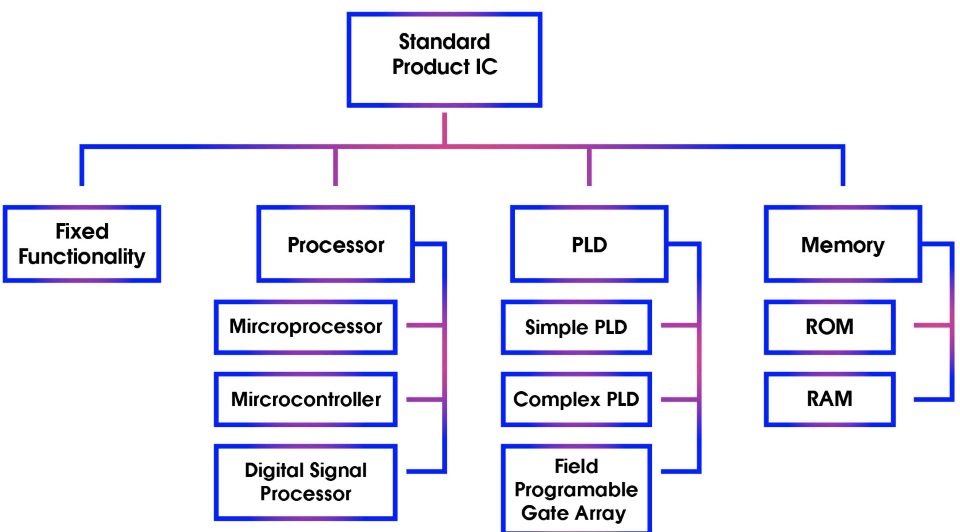

Hình 2: Các loại thiết bị kỹ thuật số có thể lập trình

Mạch tích hợp dùng cho điều khiển số và xử lý tín hiệu thường bao gồm bộ xử lý, mạch logic và bộ nhớ. Mỗi mô-đun này có thể được thực hiện bằng các công nghệ khác nhau. Các tùy chọn khả dụng được hiển thị trong hình sau:

Hình 3: Các mô-đun trong IC kỹ thuật số

Giới thiệu về CPLD

Như đã thảo luận trước đó, có nhiều loại PLD (thiết bị logic lập trình) khác nhau, chẳng hạn như FPGA, CPLD và SPLD. Sự khác biệt chính giữa các thiết bị này nằm ở độ phức tạp của mạch và số lượng ô logic khả dụng. Một SPLD thường bao gồm vài trăm cổng, trong khi CPLD bao gồm vài nghìn cổng logic.

Xét về độ phức tạp, CPLD (thiết bị logic lập trình phức tạp) nằm giữa SPLD (thiết bị logic lập trình đơn giản) và FPGA, do đó thừa hưởng các tính năng từ cả hai thiết bị này. CPLD phức tạp hơn SPLD nhưng ít phức tạp hơn FPGA.

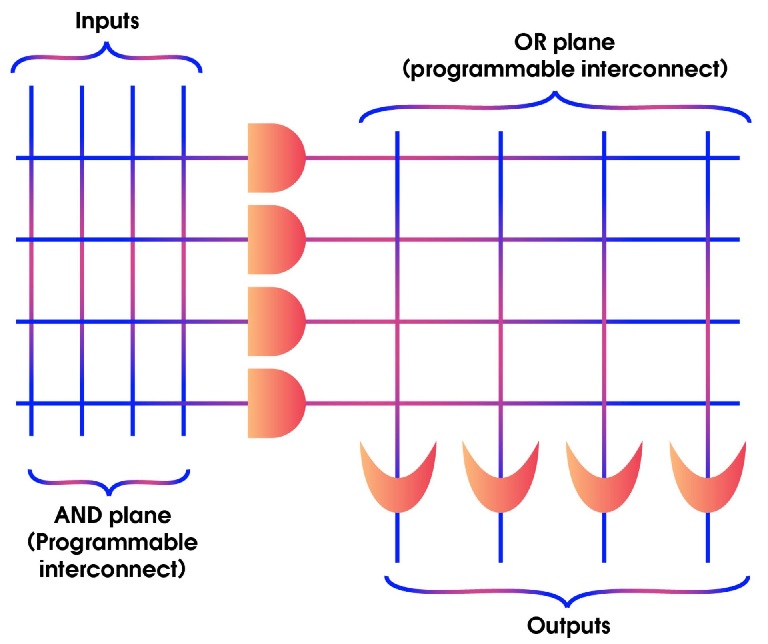

Các SPLD được sử dụng nhiều nhất bao gồm PAL (logic mảng lập trình được), PLA (logic mảng lập trình được) và GAL (logic mảng chung). PLA bao gồm một mặt phẳng AND và một mặt phẳng OR. Chương trình mô tả phần cứng xác định kết nối giữa các mặt phẳng này. Minh họa về PLA được cung cấp như sau:

Hình 4: Mảng logic lập trình (PLA)

PAL khá giống PLA, tuy nhiên chỉ có một mặt phẳng lập trình được thay vì hai (mặt phẳng AND). Bằng cách cố định một mặt phẳng, độ phức tạp của phần cứng được giảm bớt. Tuy nhiên, lợi ích này phải đánh đổi bằng tính linh hoạt.

Hình 5: Logic mảng lập trình (PAL)

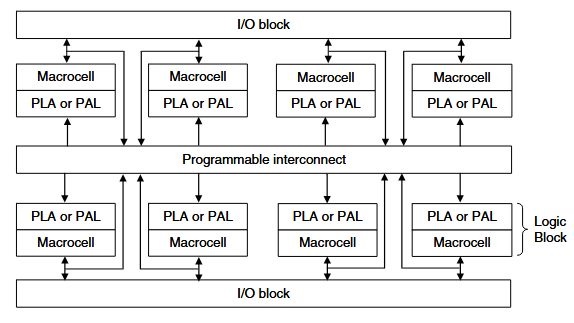

Kiến trúc CPLD

CPLD có thể được coi là một sự phát triển của PAL và bao gồm nhiều cấu trúc PAL được gọi là macrocell. Trong gói CPLD, tất cả các chân đầu vào đều có sẵn cho mỗi macrocell, trong khi mỗi macrocell có một chân đầu ra chuyên dụng. Sơ đồ khối của CPLD được minh họa như sau.

Hình 6: Sơ đồ khối CPLD

Từ sơ đồ khối, chúng ta có thể thấy một CPLD bao gồm nhiều macrocell hoặc khối chức năng. Các macrocell được kết nối thông qua một kết nối lập trình được, còn được gọi là GIM (ma trận kết nối toàn cục). Bằng cách cấu hình lại GIM, các mạch logic khác nhau có thể được thực hiện. CPLD tương tác với thế giới bên ngoài thông qua các cổng I/O kỹ thuật số.

Sự khác biệt giữa CPLD và FPGA

Trong những năm gần đây, FPGA đã trở nên rất phổ biến trong việc thiết kế các hệ thống kỹ thuật số lập trình. Có rất nhiều điểm tương đồng cũng như khác biệt giữa CPLD và FPGA. Về điểm tương đồng, cả hai đều là thiết bị logic lập trình được bao gồm các mảng cổng logic. Cả hai thiết bị đều được lập trình bằng các HDL như Verilog HDL hoặc VHDL.

Sự khác biệt đầu tiên giữa CPLD và FPGA nằm ở số lượng cổng. Một CPLD chứa vài nghìn cổng logic, trong khi số lượng cổng trong FPGA có thể lên tới hàng triệu. Do đó, các mạch và hệ thống phức tạp có thể được thực hiện bằng FPGA. Nhược điểm của sự phức tạp này là chi phí cao hơn. Do đó, CPLD phù hợp hơn cho các ứng dụng ít phức tạp hơn.

Một điểm khác biệt quan trọng nữa giữa hai thiết bị này là CPLD được tích hợp sẵn bộ nhớ EEPROM (bộ nhớ truy cập ngẫu nhiên có thể lập trình và xóa bằng điện) không bay hơi, trong khi FPGA sử dụng bộ nhớ dễ bay hơi. Nhờ đó, CPLD có thể lưu trữ nội dung ngay cả khi tắt nguồn, trong khi FPGA không thể lưu trữ nội dung. Hơn nữa, nhờ bộ nhớ không bay hơi tích hợp, CPLD có thể hoạt động ngay sau khi bật nguồn. Mặt khác, hầu hết FPGA đều yêu cầu luồng bit từ bộ nhớ không bay hơi bên ngoài để khởi động.

Về hiệu năng, FPGA có độ trễ xử lý tín hiệu khó lường do kiến trúc phức tạp kết hợp với lập trình tùy chỉnh của người dùng. Trong CPLD, độ trễ giữa các chân nhỏ hơn đáng kể do kiến trúc đơn giản hơn. Độ trễ xử lý tín hiệu là một yếu tố quan trọng cần cân nhắc khi thiết kế các ứng dụng nhúng thời gian thực và quan trọng về an toàn.

Do tần số hoạt động cao hơn và các phép toán logic phức tạp hơn, một số FPGA có thể tiêu thụ nhiều điện năng hơn CPLD. Do đó, quản lý nhiệt là một yếu tố quan trọng cần cân nhắc trong các hệ thống dựa trên FPGA. Vì lý do này, các hệ thống dựa trên FPGA thường sử dụng bộ tản nhiệt và quạt làm mát, đồng thời cần nguồn điện và mạng lưới phân phối lớn hơn, phức tạp hơn.

Xét về mặt bảo mật thông tin, CPLD an toàn hơn vì bộ nhớ được tích hợp sẵn trong chip. Ngược lại, hầu hết FPGA đều yêu cầu bộ nhớ ngoài không bay hơi, điều này có thể gây ra mối đe dọa bảo mật dữ liệu. Mặc dù FPGA có các thuật toán mã hóa dữ liệu, nhưng CPLD về bản chất lại an toàn hơn so với FPGA.

Ứng dụng của CPLD

CPLD được ứng dụng trong nhiều mạch điều khiển kỹ thuật số và xử lý tín hiệu có độ phức tạp từ thấp đến trung bình. Một số ứng dụng quan trọng bao gồm:

- CPLD có thể được sử dụng làm bộ nạp khởi động cho FPGA và các hệ thống lập trình khác.

- CPLD thường được sử dụng làm bộ giải mã địa chỉ và máy trạng thái tùy chỉnh trong các hệ thống kỹ thuật số.

- Do kích thước nhỏ và mức tiêu thụ điện năng thấp, CPLD lý tưởng để sử dụng trong các thiết bị kỹ thuật số cầm tay và di động .

- CPLD cũng được sử dụng trong các ứng dụng kiểm soát quan trọng về an toàn.

Nhà sản xuất CPLD

CPLD và FPGA là những thiết bị logic lập trình cao cấp, khó sản xuất. Các nhà sản xuất CPLD chính là:

- Altera (được Intel mua lại)

- Xilinx (được AMD mua lại)

- Atmel (được Microchip mua lại)

- Chất bán dẫn dạng lưới

Lập trình và Phát triển CPLD

Bước đầu tiên trong việc phát triển hệ thống số dựa trên CPLD là lựa chọn nhà sản xuất thiết bị. Như đã mô tả trước đó, các thiết bị này được sản xuất bởi nhiều nhà sản xuất. Sau khi tham khảo các yêu cầu của dự án và bảng dữ liệu thiết bị, cần lựa chọn thiết bị phù hợp. Các yếu tố quyết định bao gồm chi phí, mức tiêu thụ điện năng, số lượng I/O và macrocell, điện áp hoạt động và đặc tính nhiệt.

Sau khi chọn mô hình CPLD, bước tiếp theo là thiết lập môi trường lập trình và thử nghiệm. Môi trường này bao gồm một gói phần mềm được sử dụng để thiết kế, thử nghiệm và kiểm chứng mạch. Ví dụ về phần mềm lập trình bao gồm Altera Quartus, Xilinx ISE/Vivado, Lattice Diamond và Atmel ProChip Designer. Các gói phần mềm này cho phép phát triển chương trình bằng ngôn ngữ mô tả phần cứng Verilog và VHDL.

Sau khi tạo mô tả logic trong HDL, thiết bị phần cứng/bo mạch phát triển kết nối với phần mềm thông qua bộ chuyển đổi cáp lập trình và gỡ lỗi. Nhiều bo mạch phát triển có thiết bị lập trình tích hợp. Tuy nhiên, nếu không có thiết bị lập trình, bạn có thể sử dụng bộ lập trình JTAG.

Sau khi thiết kế, thử nghiệm và kiểm chứng chương trình CPLD, chương trình được tải xuống chip và một nguyên mẫu hệ thống có thể được sản xuất. Một PCB chứa CPLD và các linh kiện điện tử xung quanh có thể được thiết kế. Sau khi tích hợp, thiết bị được kiểm tra lỗi và sai sót. Sau khi gỡ lỗi, nguyên mẫu đã sẵn sàng để đưa vào sản xuất.

Điện tử số là xương sống của công nghệ thông tin hiện đại. Khả năng lập trình là một yếu tố then chốt trong thiết kế hệ thống số. Thiết bị số lập trình được chia thành hai loại: bộ xử lý và PLD. PLD mang lại hiệu suất và tính linh hoạt vượt trội nhờ phần cứng có thể cấu hình lại. CPLD là một trong ba loại PLD chính, cùng với SPLD và FPGA. Về hiệu suất và độ phức tạp, CPLD nằm giữa SPLD và FPGA. Với EEPROM không mất dữ liệu tích hợp, CPLD có lợi thế về bảo mật dữ liệu và tốc độ khởi động được cải thiện so với FPGA.

Trong bài viết này, chúng tôi cung cấp cho bạn tổng quan đầy đủ về CPLD, bao gồm kiến trúc , sơ đồ, ứng dụng và phương pháp lập trình.