Dép xỏ ngón JK (Hướng dẫn nhanh)

Trong hướng dẫn này, bạn sẽ tìm hiểu cách thức hoạt động, bảng chân lý của nó và cách xây dựng một bảng chân lý bằng cổng logic.

JK Flip-Flop là một loại flip-flop có thể được thiết lập, khởi động lại và chuyển đổi. Nó có thể được sử dụng để chế tạo bộ đếm, bộ phát hiện sự kiện, bộ chia tần số và nhiều ứng dụng khác.

Trong hướng dẫn này, bạn sẽ tìm hiểu cách thức hoạt động, bảng chân lý của nó và cách xây dựng một bảng chân lý bằng cổng logic.

Dép JK Flip-Flop là gì?

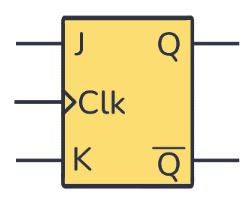

Flip-flop là linh kiện có thể lưu trữ giá trị số ở đầu ra. Chúng có ngõ vào Clock (Clk) xác định thời điểm có thể thay đổi trạng thái đầu ra.

Trái với những gì bạn nghĩ, hai đầu vào của JK Flip-Flop, “J” và “K”, không phải là viết tắt của chức năng của các chân (tương tự như chốt SR). Chúng được Jack Kilby (JK) - nhà phát minh ra nó - lựa chọn để phân biệt thiết kế flip-flop của ông với các loại khác.

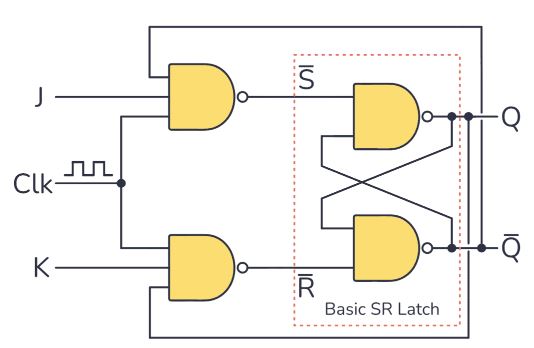

Bạn có thể xem sơ đồ triển khai cơ bản của mạch bên dưới. Mạch này dựa trên chốt SR và được xây dựng bằng cổng NAND :

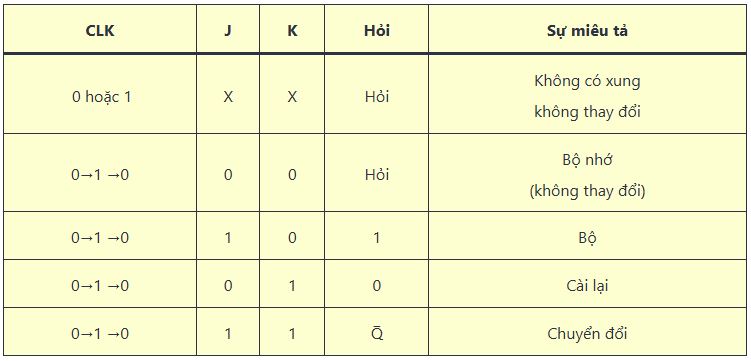

Đầu vào J và K của flip-flop JK có thể được sử dụng để thiết lập, khởi động lại hoặc chuyển đổi đầu ra, như sau:

- J=1 và K=0 đặt đầu ra thành 1

- J=0 và K=1 đặt lại đầu ra về 0

- J=1 và K=1 chuyển đổi đầu ra

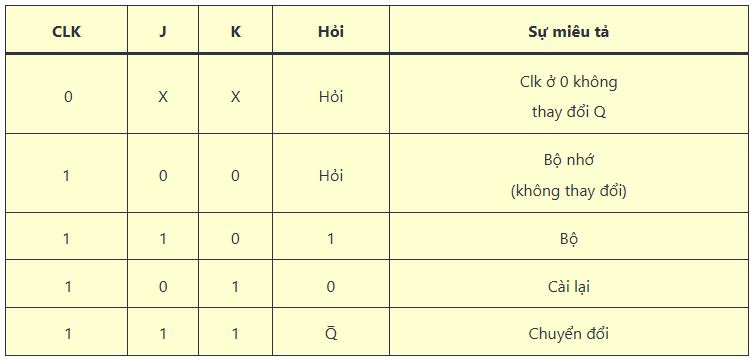

Nhưng để flip-flop thực hiện bất kỳ thay đổi nào, đầu vào Clock của nó phải là 1. Hãy xem bảng chân lý bên dưới:

Một cách thay thế để thực hiện mạch lật JK cơ bản là sử dụng hai cổng AND và hai cổng NOR như sau (nó hoạt động chính xác như mạch được xây dựng bằng cổng NAND):

Vấn đề đua xe

Về nguyên tắc, cách triển khai cơ bản ở trên hoạt động tốt, nhưng lại phát sinh vấn đề về thời gian. Khi đồng hồ ở mức "1" và bạn muốn chuyển đổi đầu ra, nó sẽ chuyển đổi rất nhanh giữa "1" và "0" cho đến khi đồng hồ trở về "0". Vấn đề này được gọi là tình trạng chạy đua (race condition ) .

Bạn có thể giải quyết vấn đề này bằng cách kích hoạt xung hoặc kích hoạt cạnh cho flip-flop .

JK Flip-Flop kích hoạt bằng xung

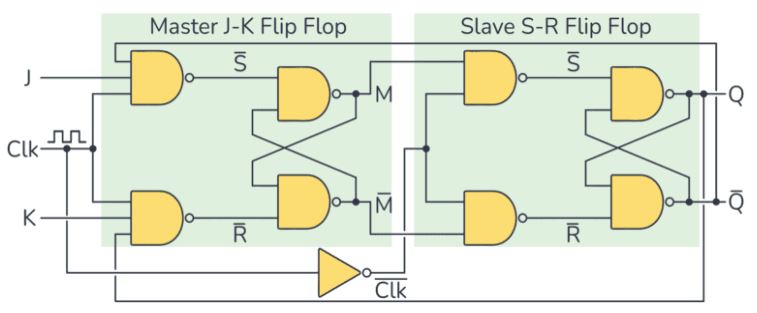

Bên dưới là một flip-flop JK được kích hoạt bằng xung dựa trên nguyên tắc Chủ-Tớ:

Như bạn có thể thấy, để xây dựng cấu hình này, bạn cần một mạch JK Flip-Flop cơ bản được kết nối với một SR flip-flop.

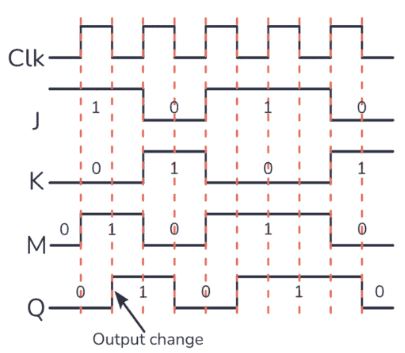

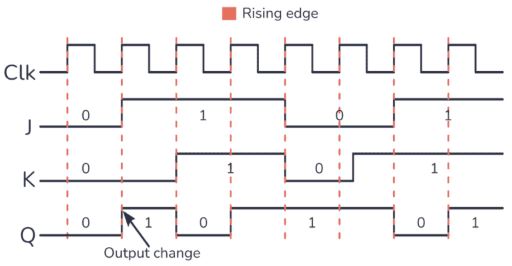

Để hiểu cách phiên bản này hoạt động, hãy xem sơ đồ thời gian bên dưới:

Ngay khi đồng hồ tạo ra cạnh lên ↑, tức là thay đổi từ 0 lên 1 (0→1), nó sẽ kích hoạt phần chính. Kết quả là, giá trị của các đầu ra trong phần này thay đổi. Các tín hiệu này được kết nối với phần phụ, nhưng không kích hoạt ở cạnh lên vì đồng hồ đã bị đảo ngược.

Khi tín hiệu xung nhịp tạo ra cạnh giảm ↓, thay đổi từ 1 thành 0 (1→0), nó sẽ kích hoạt phần phụ, khiến đầu ra Q phản ánh giá trị đầu ra của phần chính.

Vì vậy, mạch này cần một xung hoàn chỉnh (0→1→0) để thay đổi đầu ra. Đó là lý do tại sao cấu hình này được gọi là JK Flip-Flop kích hoạt bằng xung .

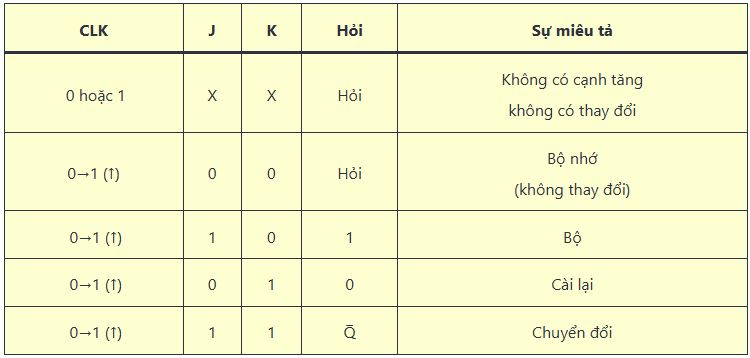

JK Flip-Flop kích hoạt cạnh

Không giống như thiết kế Master-Slave, cần có xung hoàn chỉnh, bạn cũng có thể xây dựng thiết kế kích hoạt cạnh được kích hoạt từ cạnh tăng ↑ hoặc cạnh giảm ↓.

Dưới đây là sơ đồ thời gian cho một sơ đồ kích hoạt ở cạnh tăng:

Hình ảnh trên cho thấy mạch này chỉ cần một cạnh tăng trên đầu vào Clk để thay đổi trạng thái của đầu ra Q. Và nó sẽ chỉ thay đổi ở cạnh tăng.

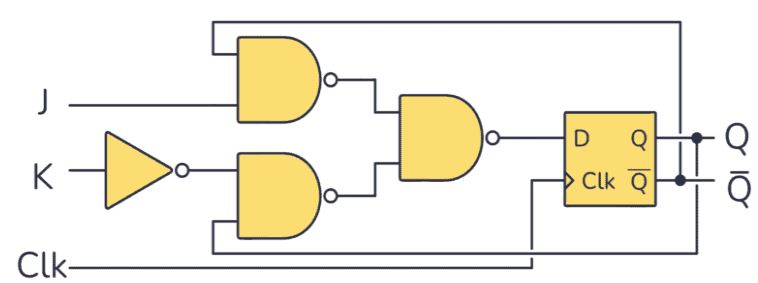

Để xây dựng một JK Flip-Flop chỉ kích hoạt với tín hiệu cạnh tăng, bạn có thể sử dụng một D flip-flop kích hoạt cạnh tăng , một cổng NOT và các cổng NAND như sau:

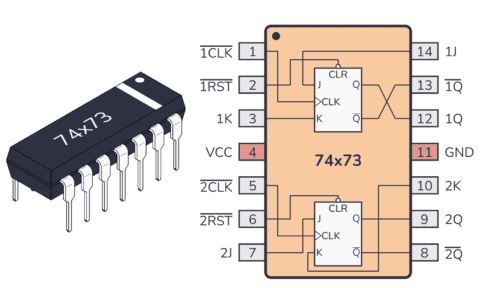

Mạch tích hợp với JK Flip-Flop

Bạn cần một JK Flip-Flop? Bạn không cần phải tự lắp ráp nó từ đầu. Có rất nhiều mạch tích hợp với mạch JK Flip-Flop bên trong. Hai lựa chọn phổ biến là chip CD4027 hoặc IC 74HC73 .