Điện trở kéo lên và kéo xuống

Hãy cùng tìm hiểu cách các điện trở kéo lên và kéo xuống giúp các mạch kỹ thuật số tránh bị nhầm lẫn bởi các tín hiệu đầu vào "không xác định".

Điện trở kéo lên là gì?

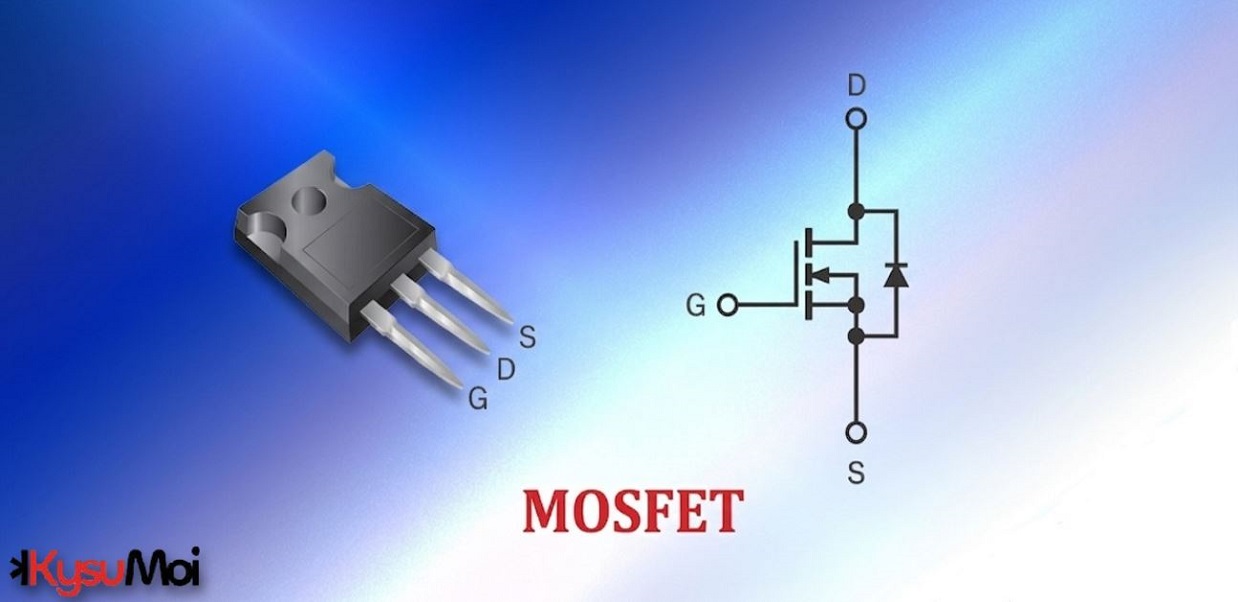

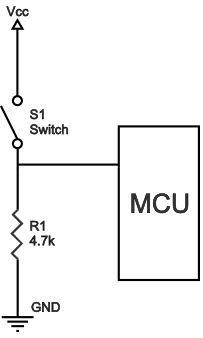

Điện trở kéo lên là một điện trở được sử dụng trong các mạch logic để đảm bảo rằng mức logic được xác định rõ ràng luôn hiện diện tại một chân trong mọi điều kiện. Hãy nhớ rằng các mạch logic kỹ thuật số có ba trạng thái logic: cao, thấp và trạng thái nổi (hoặc trở kháng cao). Trạng thái trở kháng cao xảy ra khi một chân không được kéo lên mức logic cao hoặc thấp, mà thay vào đó được để "nổi". Một ví dụ điển hình của vấn đề này là một chân đầu vào không được kết nối của vi điều khiển, không ở trạng thái logic cao hay thấp, và vi điều khiển có thể hiểu nhầm giá trị đầu vào là giá trị logic cao hoặc thấp. Điện trở kéo lên được sử dụng để giải quyết vấn đề này cho vi điều khiển bằng cách kéo giá trị lên trạng thái logic cao, như hình ảnh sau đây.

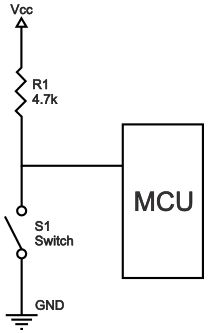

Nếu không có điện trở kéo lên, tín hiệu đầu vào của MCU sẽ ở trạng thái nổi khi công tắc bật và chỉ kéo xuống mức logic thấp khi công tắc tắt.

Điện trở kéo lên không phải là một loại điện trở đặc biệt, mà chỉ đơn giản là một điện trở có giá trị cố định được mắc giữa nguồn điện áp (thường là +5 V, +3.3 V hoặc +2.5 V) và một đầu nối phù hợp. Điều này cho phép áp dụng điện áp đầu vào hoặc đầu ra đã được xác định trước ngay cả khi không có tín hiệu điều khiển. Giá trị điện trở kéo lên điển hình là 4.7 kΩ, nhưng giá trị này có thể thay đổi tùy thuộc vào ứng dụng, như sẽ được thảo luận thêm trong bài viết này.

Định nghĩa về điện trở kéo lên.

Điện trở kéo lên là một điện trở được sử dụng để đảm bảo đường dây được kéo lên mức logic cao khi không có tín hiệu đầu vào.

Điện trở kéo xuống là gì?

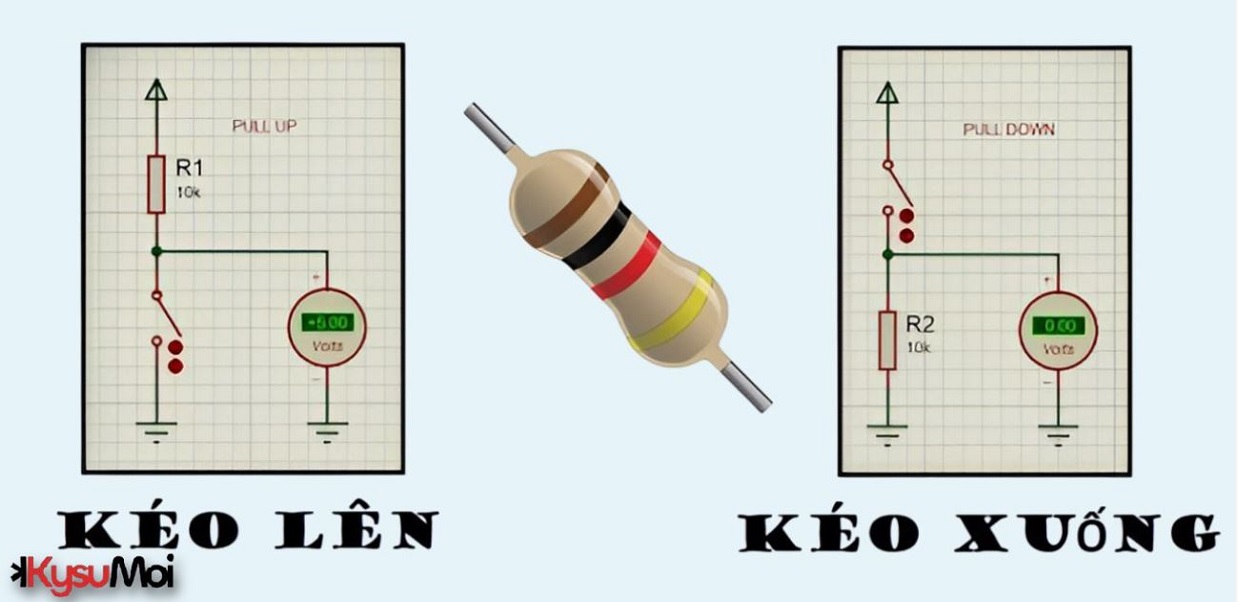

Điện trở kéo xuống hoạt động tương tự như điện trở kéo lên, ngoại trừ việc điện trở kéo xuống làm giảm mức tín hiệu logic của một chân. Điện trở này được kết nối giữa điểm nối đất và chân tương ứng trên thiết bị. Một ví dụ về điện trở kéo xuống trong mạch kỹ thuật số có thể được thấy trong hình sau.

Trong sơ đồ này, một công tắc nhấn được kết nối giữa điện áp và các chân đầu vào của vi điều khiển. Trong một mạch như thế này, khi công tắc đóng, đầu vào của vi điều khiển có giá trị logic cao. Tuy nhiên, khi công tắc mở, một điện trở kéo xuống sẽ kéo điện áp đầu vào xuống đất (logic 0) để ngăn chặn các trạng thái đầu vào không ổn định. Điện trở kéo xuống phải có điện trở lớn hơn trở kháng của mạch logic; nếu không, nó có thể kéo xuống quá nhiều điện áp, và điện áp đầu vào tại các chân sẽ duy trì ở giá trị logic thấp không đổi bất kể vị trí của công tắc.

Giá trị điện trở kéo lên và kéo xuống.

Giá trị tối ưu của điện trở kéo lên (hoặc kéo xuống) bị giới hạn bởi hai yếu tố. Thứ nhất là tổn thất công suất. Nếu điện trở quá thấp, dòng điện cao sẽ chạy qua điện trở kéo lên, khiến thiết bị nóng lên và tiêu thụ công suất không cần thiết khi công tắc đóng. Tình trạng này được gọi là kéo lên mạnh và nên tránh khi yêu cầu tiêu thụ điện năng thấp. Yếu tố thứ hai là điện áp đầu vào khi công tắc mở. Nếu điện trở kéo lên quá cao, kết hợp với dòng rò lớn ở đầu vào, điện áp đầu vào có thể không đủ khi công tắc mở. Tình trạng này được gọi là kéo lên yếu. Điện trở kéo lên thực tế phụ thuộc vào trở kháng đầu vào, có liên quan chặt chẽ đến dòng rò ở đầu cực.

Nguyên tắc cơ bản là sử dụng điện trở kéo lên có giá trị nhỏ hơn ít nhất 10 lần trở kháng đầu vào. Trong các mạch logic lưỡng cực hoạt động ở điện áp 5 volt, giá trị điện trở kéo lên điển hình là 1-5 kΩ. Đối với các ứng dụng chuyển mạch và cảm biến điện trở, giá trị điện trở kéo lên điển hình là 1-10 kΩ. Nếu không chắc chắn, điểm khởi đầu tốt khi sử dụng công tắc là 4,7 kΩ. Một số mạch kỹ thuật số, chẳng hạn như mạch CMOS, có dòng rò đầu vào nhỏ, cho phép sử dụng các giá trị điện trở cao hơn nhiều, dao động từ khoảng 10 kΩ đến 1 MΩ. Nhược điểm của việc sử dụng các giá trị điện trở cao hơn là đầu vào phản hồi chậm với sự thay đổi điện áp, do sự ghép nối giữa điện trở kéo lên và tổng điện dung của các chân và dây dẫn tại nút chuyển mạch, tạo nên mạch RC. Tích của R và C càng lớn, thời gian để điện dung nạp và xả càng lâu, dẫn đến hoạt động mạch chậm hơn. Trong các mạch tốc độ cao, điện trở kéo lên lớn đôi khi có thể hạn chế tốc độ mà một chân có thể thay đổi trạng thái một cách đáng tin cậy.

Các ứng dụng điển hình của điện trở kéo lên và kéo xuống.

Điện trở kéo lên và kéo xuống thường được sử dụng khi kết nối các công tắc hoặc các đầu vào khác với vi điều khiển hoặc các cổng logic số khác. Hầu hết các vi điều khiển đều có điện trở kéo lên và/hoặc kéo xuống tích hợp có thể lập trình được, giúp giảm số lượng linh kiện bên ngoài. Các công tắc có thể được kết nối trực tiếp với các vi điều khiển này. Nói chung, điện trở kéo lên được sử dụng thường xuyên hơn điện trở kéo xuống, mặc dù một số dòng vi điều khiển cung cấp cả hai tùy chọn kéo lên và kéo xuống.

Nó thường được sử dụng để kiểm soát dòng điện chạy vào cảm biến điện trở trước khi chuyển đổi tín hiệu điện áp đầu ra của cảm biến từ dạng tương tự sang dạng kỹ thuật số.

Một ứng dụng khác là giao thức bus I2C, sử dụng điện trở kéo lên để cho phép một chân duy nhất hoạt động như một đầu vào hoặc đầu ra. Khi không được kết nối với bus, chân này ở trạng thái trở kháng cao.

Điện trở kéo xuống cũng được sử dụng với các đầu ra để thu được trở kháng đầu ra đã biết.