Ghép nối nhiễu nền trong mạch tích hợp

Bài viết này xem xét các cơ chế và kỹ thuật giảm thiểu nhiễu nền, một vấn đề quan trọng ảnh hưởng đến tính toàn vẹn của tín hiệu trong Mạch tích hợp.

Mạch tích hợp silicon sử dụng nhiều hình thức cách ly khác nhau để cách ly điện các thiết bị, chẳng hạn như tiếp giáp PN phân cực ngược hoặc cách ly rãnh. Ngoại trừ các vật liệu đặc biệt như silicon trên sapphire, tất cả đều sử dụng đế silicon, vốn là một đường dẫn tiềm ẩn cho hiện tượng ghép nhiễu. Sự ghép nhiễu này có thể làm giảm hiệu suất hoặc thậm chí gây ra lỗi chức năng. Vì vậy, các nhà thiết kế cần sử dụng nhiều kỹ thuật khác nhau để giảm thiểu ghép nhiễu.

Có nhiều loại chất nền khác nhau điển hình:

- Điện trở suất cao; được sử dụng cho RF khi cần mức suy hao thấp cho các thiết bị như cuộn cảm và tụ điện trên chip.

- Epi loại P được phát triển trên nền P+ thường được sử dụng cho logic kỹ thuật số. Sự kết hợp giữa nền có điện trở suất thấp, mang lại khả năng bảo vệ chốt, và epi có điện trở suất cao hơn cho hiệu suất thiết bị là hoàn toàn khả thi.

- Lớp chôn có điện trở suất thấp và lớp chôn có điện trở suất cao cho các quá trình lưỡng cực.

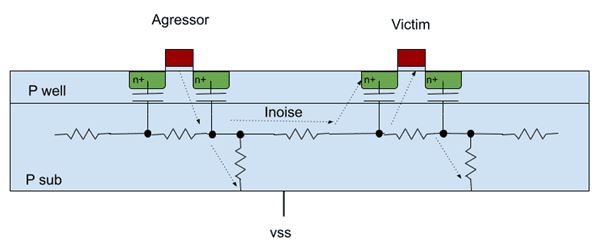

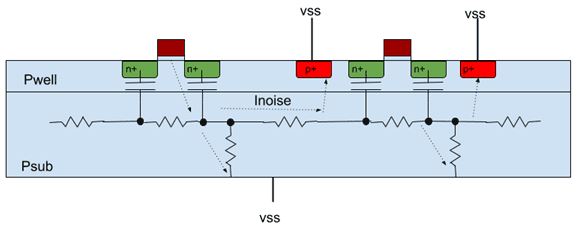

Trong Hình 1, chúng tôi trình bày một trường hợp điển hình khi có 2 thiết bị NMOS trong một đế P chung. Ở tần số đủ thấp (< 10 GHz), đế có thể được coi là hoàn toàn có điện trở, do đó, sự ghép nhiễu chủ yếu diễn ra thông qua các tiếp giáp PN và chính đế.

Trong ví dụ trên, tiếng ồn có thể được đưa vào chất nền từ một số nguồn:

- Sự ion hóa tác động trong kênh của các thiết bị MOS

- Ghép nối điện dung từ tín hiệu nhiễu qua các tiếp giáp PN

- Gói RLC gây ra hiện tượng nảy nguồn do sự thay đổi đột ngột về điện năng và hiệu ứng Ldi/dt.

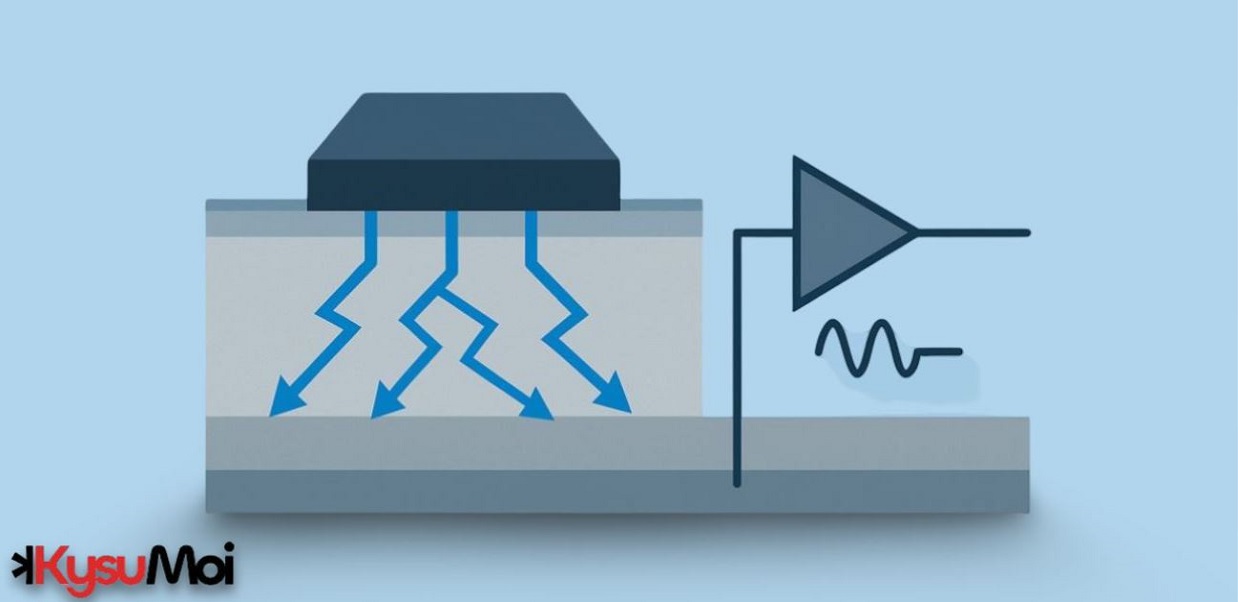

Tiếng ồn sau đó có thể truyền qua đế đến các khu vực nhạy cảm của mạch. Thông thường, tiếng ồn có thể bắt nguồn từ một khối kỹ thuật số chuyển mạch nhanh và ghép nối với một khối tương tự. Tại đó, sự dao động điện áp đế có thể khiến Vt của các thiết bị thay đổi và gây ra sự thay đổi độ khuếch đại. Các công cụ thương mại có thể phân tích sự ghép nối tiếng ồn đế, thường bằng cách xây dựng một lưới RC của đế. Biết được cấu hình pha tạp của các mối nối và giếng, điện trở suất của đế có thể được rời rạc hóa để tạo thành lưới RC, sau đó có thể được giải bằng phương pháp phần tử hữu hạn hoặc phần tử biên để tính điện áp và dòng điện theo thời gian và/hoặc tần số. Tuy nhiên, việc phân tích đầy đủ rất phức tạp và tốn thời gian, vì vậy nhiều nhà thiết kế áp dụng các kỹ thuật đã được thử nghiệm và kiểm tra để giảm thiểu các vấn đề về tiếng ồn đế.

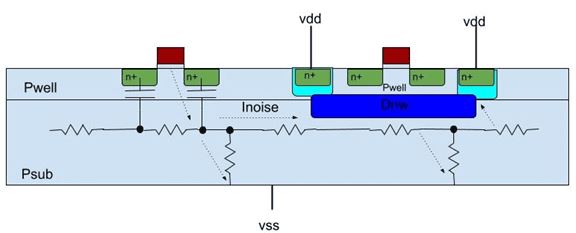

Trong trường hợp đơn giản nhất đối với các thiết bị trong chất nền P (Hình 2), vòng bảo vệ P+ xung quanh các thiết bị nhạy cảm và/hoặc xung quanh bộ truyền nhiễu có thể giảm sự ghép nối nhiễu chất nền xuống 30dB [1].

Một cách tiếp cận khác là sử dụng vòng bảo vệ NW được nối với VDD để tạo ra mối nối PN phân cực ngược (Hình 3). Điều này giúp giảm nhiễu tốt hơn, đặc biệt là ở tần số thấp, khi trở kháng của tụ điện tiếp giáp vượt trội hơn điện trở suất của nền nhưng lại chiếm diện tích lớn hơn.

Cách tiếp cận thứ ba sử dụng NW sâu để cô lập các thiết bị trong ống P riêng của chúng, mang lại khả năng cô lập thậm chí còn tốt hơn (Hình 4). Cần phải cẩn thận với lưới mà DNW được kết nối. Thoạt đầu, có vẻ như việc kết nối nó với VDD là đúng, để đảo ngược phân cực các mối nối PN. Tuy nhiên, nếu nó được kết nối với VDD chung – với các xung đột nguồn bị trầm trọng hơn do độ tự cảm của dây đóng gói hoặc dây liên kết – nó sẽ hoạt động như một bộ truyền nhiễu mạnh vào giếng P bị cô lập do điện dung mối nối diện tích lớn. Việc kết nối DNW với VSS, tốt nhất là độc lập với phần còn lại của VSS trên chip, có thể ngăn ngừa điều này.

Tóm lại, nhiễu nền là một vấn đề nghiêm trọng với mạch kỹ thuật số tốc độ cao trên cùng nền với mạch tương tự hoặc mạch RF nhạy cảm. Nhiễu nền có thể làm giảm hiệu suất hoặc thậm chí gây ra lỗi chức năng. Việc sử dụng cẩn thận các vòng bảo vệ có thể giúp giảm thiểu nhiễu nền bằng cách tăng diện tích một chút.