Giải mã bộ nhớ là gì?

Hãy tìm hiểu cách máy tính chuyển đổi mã nhị phân thô thành các vị trí vật lý cụ thể thông qua quá trình giải mã bộ nhớ.

Mạch điện tử kỹ thuật số là một loại mạch chỉ xử lý tín hiệu có hai trạng thái: hoặc không hoặc một. Transistor trong mạch được sử dụng để thực hiện các phép toán logic Boolean khác nhau.

Trong điện tử số, quá trình giải mã bộ nhớ diễn ra khi cần truy cập bộ nhớ trong các thiết bị kỹ thuật số. Trong quá trình này, các địa chỉ nhị phân được tạo ra để tìm bộ nhớ mong muốn trong hệ thống. Kết quả là, các đơn vị bộ nhớ được tạo ra, với sự trợ giúp của các địa chỉ bộ nhớ, có thể tìm thấy dữ liệu được yêu cầu. Quá trình này bao gồm nhiều bước mà chúng ta phải tuân theo để xác định chính xác vị trí bộ nhớ cần thiết.

Trong bài viết này, chúng ta sẽ thảo luận về cấu tạo bên trong của chip nhớ, quá trình giải mã và các thành phần khác nhau tham gia vào quá trình giải mã bộ nhớ.

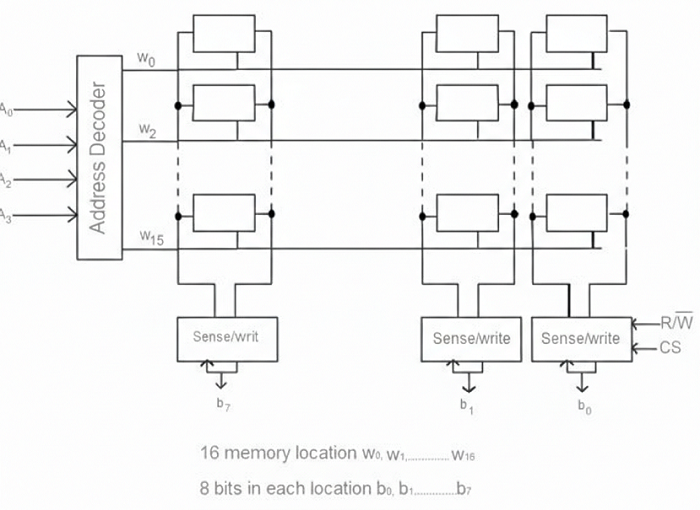

Sự hình thành nội tại của ký ức:

Trong cấu trúc bên trong, một ô nhớ nhị phân và các cơ chế giải mã liên quan để chọn một từ duy nhất tạo nên cấu trúc bên trong của bộ nhớ truy cập ngẫu nhiên (RAM) với m từ và n bit trên mỗi từ . Trong đơn vị bộ nhớ, khối xây dựng cơ bản là một ô nhớ nhị phân.

Trong một ô nhớ, một bit thông tin duy nhất có thể dễ dàng được lưu trữ. Chip nhớ được tạo thành từ nhiều ô được sắp xếp theo ma trận.

Một từ nhớ được tạo ra bởi mỗi hàng ô, và mỗi hàng ô được kết nối với một đường chung, còn được gọi là đường từ . Đường từ được điều khiển bởi một bộ giải mã địa chỉ. Tùy thuộc vào địa chỉ có trong bus địa chỉ, một đường từ được kích hoạt tại bất kỳ thời điểm nào. Hai đường chạy giữa các ô trong mỗi cột. Chúng được gọi là các đường bit. Một mạch cảm biến/ghi kết nối các đường bit này với các đường dữ liệu đầu vào và đầu ra. Mạch cảm biến/ghi cảm nhận, hoặc đọc, thông tin chứa trong các ô được chỉ định bởi một đường từ và truyền nó đến đường dữ liệu đầu ra trong các hoạt động đọc. Mạch cảm biến/ghi nhận thông tin trong quá trình ghi.

Để hiểu rõ cấu tạo bên trong của chip nhớ, bạn có thể xem sơ đồ bên dưới:

Quá trình giải mã bộ nhớ:

Quá trình giải mã bộ nhớ là một quá trình nhiều bước, trong đó nhiều địa chỉ được sử dụng để xác định vị trí bộ nhớ cụ thể. Giải mã bộ nhớ diễn ra khi cần truy cập vào bộ nhớ được lưu trữ trong thiết bị điện tử kỹ thuật số. Trong quá trình sau...

Bộ giải mã bộ nhớ là cần thiết để chọn các địa chỉ đầu vào được chỉ định từ bộ nhớ trong đơn vị bộ nhớ. Tại đây, ô nhớ đóng vai trò quan trọng trong quá trình này.

Ô nhớ: Ô nhớ là một loại mạch điện, chứa từ bốn đến sáu transistor. Đầu vào được chọn giúp ô nhớ dễ dàng thực hiện các thao tác đọc/ghi. Trong quá trình này, bằng cách tạo một đường dẫn từ chốt đến đầu ra, A1 ở đầu vào đọc/ghi thực hiện thao tác đọc. Mặt khác, bằng cách xây dựng đường dẫn từ đầu vào đến chốt, A0 ở đầu vào đọc/ghi có thể thực hiện thao tác ghi.

Về cấu tạo của ô nhớ, thông thường, ô nhớ có khả năng lưu trữ các tín hiệu nhị phân theo các đơn vị khác nhau, được gọi là bit. Ban đầu, một bit bằng 8 bit, và một từ có giá trị là 2 bit. Các đường dữ liệu đầu vào và đầu ra giao tiếp với nhau trong bộ nhớ thông qua các thao tác đọc/ghi. Ban đầu, nó giúp xác định việc truyền tải thông tin. Trong bộ nhớ, mỗi từ có một số, được gọi là địa chỉ. Các địa chỉ này nằm trong khoảng từ 0 đến 2k-1. Ở đây, k là số thứ tự của đường địa chỉ.

Nhìn chung, một RAM nhỏ bao gồm bốn từ, mỗi từ bốn bit và tổng cộng 16 ô nhị phân. Ô nhị phân, cùng với ba đầu vào và một đầu ra, tạo thành một khối ô nhỏ (BC). Ở đây, người dùng cần hai đường địa chỉ cho bốn từ bộ nhớ. Để chọn một trong bốn từ, các đầu vào địa chỉ cần đi qua bộ giải mã 2:4, có thể được kích hoạt thông qua đầu vào kích hoạt bộ nhớ.

Tiếp tục quá trình, trong điều kiện giá trị bộ nhớ được kích hoạt là 0, tất cả các đầu ra trong bộ giải mã đều được đặt về 0 và không có đầu ra nào được chọn. Và nếu giá trị bộ nhớ được chọn là 1, thì 1 trong 4 từ sẽ được chọn.

Quá trình đọc/ghi: Tại đây, sau khi chọn từ, dữ liệu đầu vào đọc/ghi sẽ được xử lý. Trong quá trình đọc, bốn bit của từ được chọn sẽ đi qua các cổng OR đến các đầu ra.

Mặt khác, trong thao tác ghi, dữ liệu có sẵn trong các dòng đầu vào được chuyển vào bốn ô nhị phân từ từ được chọn. Trong quá trình này, các ô không được chọn sẽ trở thành ô giả và giá trị của chúng vẫn được giữ nguyên.

Giải mã địa chỉ bộ nhớ:

Trong bộ nhớ truy cập ngẫu nhiên (RAM) , có một không gian trống, nơi có hàng ngàn địa chỉ từ khả dụng. Mỗi từ bộ nhớ có một giá trị, nằm trong khoảng từ 1 đến 64 bit. Ở đây, một bộ nhớ có 2000 từ sử dụng k đường địa chỉ bộ nhớ với n bit cho mỗi từ bộ nhớ. Bộ giải mã bao gồm 2000 địa chỉ bộ nhớ, trong đó mỗi địa chỉ được giải mã xuất ra xác định một từ n bit duy nhất để đọc hoặc ghi tiếp.

Ở đây, đường địa chỉ biểu thị dữ liệu đầu vào, được gọi là mã, các đầu ra biểu thị tín hiệu từ, có thể là mức cao hoặc mức thấp. Trong máy tính cá nhân và bộ vi xử lý, có một chip nhớ được định vị, và mỗi chip có một đầu vào được chọn. Bây giờ, để chọn, cần phải chỉ định chip nhớ.

Khi chỉ một chip được chọn và vận hành đồng thời, người dùng có thể chọn đúng thiết bị mã hóa địa chỉ bộ nhớ cho một vị trí địa chỉ bộ nhớ nhất định.

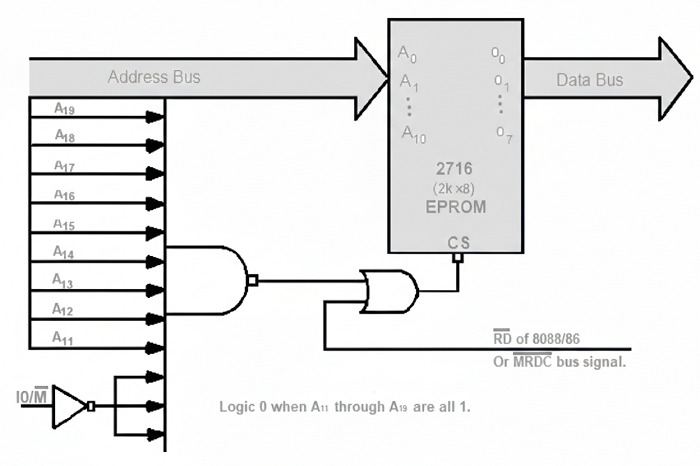

Ví dụ: Bây giờ, hãy lấy ví dụ bộ vi xử lý 8088, tạo ra các địa chỉ 20 bit cho không gian địa chỉ bộ nhớ 1MB làm đầu ra. Mặt khác, một EPROM BIOS 2716 chỉ có 2KB bộ nhớ cùng với 11 chân địa chỉ. Ở đây, EPROM có thể được đặt trong bất kỳ phần 2KB nào của không gian địa chỉ 1MB, vì bộ giải mã ở đây có thể giải mã 9 chân địa chỉ bổ sung.

Điều này có thể được hiểu rõ hơn thông qua sơ đồ sau:

Giải mã trùng hợp:

Trong phương pháp giải mã đồng thời, bộ giải mã với k đầu vào tạo ra đầu ra có giá trị 2k. Loại bộ giải mã này yêu cầu 2k cổng AND, cùng với k đầu vào ở mỗi cổng. Ở đây, bằng cách kết hợp hai bộ giải mã thành một sơ đồ hai chiều, tổng số cổng và số đầu vào trên mỗi cổng có thể được giảm bớt.

Ngoài ra, trong phương pháp ma trận hai chiều, một bộ giải mã được sử dụng để chọn hàng và bộ còn lại để chọn cột. Trong trường hợp này, hai đầu vào 2k được sử dụng thay vì một đầu vào k.

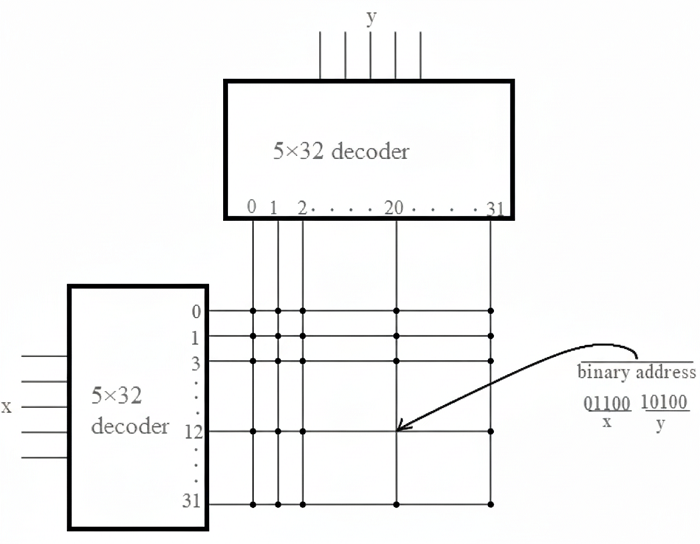

Điều này có thể được hiểu rõ hơn thông qua sơ đồ sau:

Ví dụ: Ở đây, thay vì sử dụng bộ giải mã 10 x 1024 trong phương pháp lựa chọn cho bộ nhớ 1K từ, có thể chọn hai bộ giải mã 5 x 32. Chúng ta cần 1024 cổng AND với mười đầu vào mỗi cổng trong một bộ giải mã duy nhất.

Trong trường hợp có hai bộ giải mã, chúng ta sẽ cần 64 cổng AND, mỗi cổng có năm đầu vào. Năm bit quan trọng nhất được gán cho đầu vào X, và năm bit ít quan trọng nhất được gán cho đầu vào Y. Mỗi từ trong mảng bộ nhớ được chọn là kết quả của sự trùng khớp giữa một dòng X và một đầu vào Y.

Kết quả là, một từ duy nhất trong bộ nhớ được chọn bằng hệ số trùng khớp giữa 1 trong 32 hàng và 1 trong 32 cột, tổng cộng có gần 1.024 từ. Từ cần thiết được tìm thấy tại giao điểm của một hàng và một cột cụ thể. Sau đó, tất cả các bit của từ cần thiết được đọc/ghi.

Ghép kênh địa chỉ:

Kỹ thuật ghép kênh địa chỉ cho phép người dùng sử dụng ít chân hơn, và kết quả là chỉ cần sử dụng một vài đường truyền trên bộ xử lý. Thay vì có các đường truyền riêng biệt cho địa chỉ và dữ liệu, địa chỉ có thể được đặt trên đường truyền dữ liệu, nơi dữ liệu được đọc và lưu tại địa chỉ đã đọc trước đó.

Cụ thể, bộ nhớ SRAM (Static Random Access Memory ) có sáu bóng bán dẫn . Khi kích thước của các bóng bán dẫn nhỏ hơn, các ô nhớ mật độ cao sẽ được tạo ra.

DRAM, hay bộ nhớ truy cập ngẫu nhiên động , cũng bao gồm một bóng bán dẫn, cho phép nó có dung lượng lưu trữ bộ nhớ lớn hơn SRAM. Lưu trữ dữ liệu bằng SRAM đắt hơn lưu trữ dữ liệu bằng DRAM. DRAM tiết kiệm năng lượng hơn.

Vì kích thước bit của từ trong DRAM là một, nên cần nhiều chip. Chủ yếu là do dung lượng tăng lên; việc giải mã tất cả các bit DRAM được thực hiện trong một mảng hai chiều, và nếu có nhiều dữ liệu bộ nhớ trong một ô, thì cần nhiều mảng hơn. Kỹ thuật ghép kênh địa chỉ được các nhà thiết kế sử dụng để giảm số lượng chân trong các mạch tích hợp.

Ở đây, địa chỉ được chia thành hai phần cho các nhóm thời gian riêng biệt trong mảng hai chiều. Địa chỉ của các hàng được liệt kê trước, tiếp theo là địa chỉ của các cột. Kích thước tổng thể được giảm bớt một cách có chủ đích vì cùng một bộ chân được sử dụng cho cả hai phía của địa chỉ bộ nhớ.

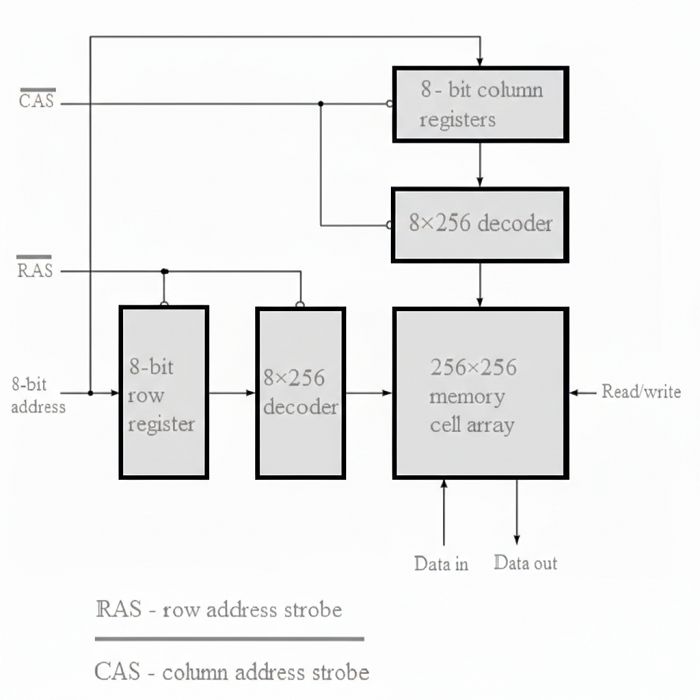

Ví dụ: Trong ghép kênh, cần bộ nhớ 64K từ. Mảng hai chiều các ô được tổ chức thành 256 hàng và 256 cột, tạo thành địa chỉ bộ nhớ. Điều này cho tổng cộng 64K từ bộ nhớ. Có hai xung địa chỉ, một đường vào dữ liệu, một đường ra dữ liệu, một điều khiển đọc/ghi với đầu vào địa chỉ 8 bit và một đường vào dữ liệu khác. Xung địa chỉ hàng được viết tắt là RAS, kích hoạt thanh ghi hàng bộ nhớ 8 bit. Xung địa chỉ cột bị cắt bớt vì CAS kích hoạt thanh ghi cột 8 bit. Ký hiệu xung có một thanh ngang ở trên, cho biết các thanh ghi đang trống hoặc ở mức tín hiệu 0.

Điều này có thể được hiểu rõ hơn qua sơ đồ sau:

Sơ đồ ghép kênh địa chỉ

Cho đến nay, chúng ta đã tìm hiểu về cấu trúc bên trong và quy trình giải mã bộ nhớ, cùng với các khía cạnh khác nhau của việc giải mã trong bài viết này. Cuối cùng, chúng ta có thể khẳng định rằng giải mã bộ nhớ là một khía cạnh quan trọng nhưng cơ bản trong việc truy cập bộ nhớ của mạch điện tử kỹ thuật số.