Giải thích về Quét ranh giới (JTAG/IEEE 1149.1)

Tìm hiểu cách thức hoạt động của quét ranh giới JTAG và lý do tại sao chúng trở nên không thể thiếu trong thử nghiệm PCB.

Trong thế giới điện tử phức tạp, việc đảm bảo hiệu suất hoàn hảo và xác định chính xác lỗi trên Bảng mạch in (PCB) vừa là thách thức vừa là nhu cầu cấp thiết. Khi thiết kế điện tử ngày càng phức tạp, các phương pháp kiểm tra truyền thống thường không đáp ứng được yêu cầu. Đây chính là lúc công nghệ Quét ranh giới JTAG ra đời, mang đến một giải pháp mạnh mẽ và sáng tạo cho các kỹ sư và nhà sản xuất trên toàn thế giới.

PCB hiện đại đòi hỏi các phương pháp kiểm tra thông minh hơn

Khi thiết kế PCB phát triển, các công cụ kiểm tra truyền thống như máy kiểm tra dạng giường đinh gặp phải những hạn chế đáng kể. Các kết nối dày đặc, bo mạch nhiều lớp và việc thiếu các điểm truy cập vật lý khiến việc xác định lỗi bằng các phương pháp cũ gần như không thể. Điểm nghẽn này đặt ra một thách thức quan trọng cho các nhà phát triển: làm thế nào để kiểm tra PCB hiệu quả và chính xác mà không ảnh hưởng đến chi phí hoặc thời gian? Câu trả lời nằm ở công nghệ quét ranh giới JTAG, một phương pháp được chuẩn hóa bởi giao thức IEEE 1149.1. Công nghệ này cách mạng hóa việc kiểm tra bằng cách nhúng các khả năng chẩn đoán trực tiếp vào phần cứng, loại bỏ nhu cầu sử dụng các đầu dò vật lý.

Kiểm tra PCB đơn giản, không xâm lấn

Hãy tưởng tượng một quy trình kiểm tra cho phép bạn xác minh các kết nối, chẩn đoán lỗi và thậm chí lập trình thiết bị mà không cần tiếp cận vật lý với bo mạch. Đây chính là lời hứa hẹn của công nghệ quét ranh giới JTAG. Đối với các nhà phát triển, công nghệ này mang đến cơ hội mạnh mẽ để nâng cao hiệu quả, cải thiện khả năng phát hiện lỗi và rút ngắn thời gian đưa sản phẩm ra thị trường. Đây là một bước ngoặt cho các nhà sản xuất đang nỗ lực duy trì khả năng cạnh tranh trong một ngành công nghiệp mà độ chính xác và tốc độ là tối quan trọng.

Cách thức hoạt động của công nghệ quét ranh giới JTAG

Về cơ bản, quét ranh giới JTAG là một phương pháp kiểm tra PCB bằng cách nhúng các mạch chuyên dụng vào bên trong chip. Các mạch này tạo ra một "chuỗi quét" cho phép các kỹ sư kiểm soát và quan sát tín hiệu tại mỗi chân đầu vào và đầu ra. Dưới đây là cái nhìn sâu hơn về cách thức hoạt động của nó:

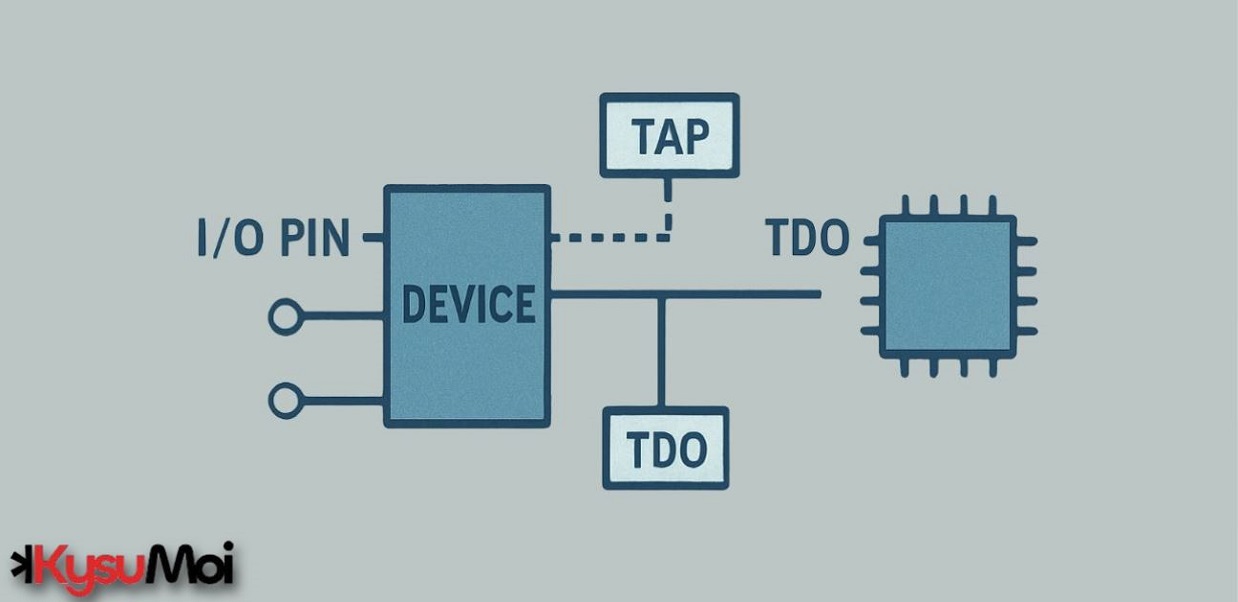

Cổng Truy cập Kiểm tra (TAP): Kiến trúc JTAG bao gồm một Cổng Truy cập Kiểm tra, một giao diện chuẩn hóa giao tiếp với thiết bị kiểm tra bên ngoài. Cổng này đóng vai trò là điểm vào cho tất cả các hoạt động quét ranh giới.

Các ô quét ranh giới: Được nhúng dọc theo các chân I/O, các ô này thu thập và xử lý tín hiệu, cho phép thực hiện các bài kiểm tra mà không cần tiếp cận vật lý đến các chân.

Chuỗi quét: Tất cả các ô quét ranh giới được kết nối với nhau theo một chuỗi nối tiếp, cho phép dữ liệu truyền tải liền mạch cho mục đích chẩn đoán hoặc lập trình.

Điều khiển thông qua phần mềm: Các công cụ như onTAP sử dụng kiến trúc này để chạy các bài kiểm tra toàn diện, xác định lỗi và lập trình thiết bị một cách chính xác.

Bằng cách tận dụng kiến trúc này, các kỹ sư có thể thực hiện các tác vụ như kiểm tra kết nối, lập trình flash và chẩn đoán nâng cao với độ chính xác đáng kinh ngạc.

Tại sao quét ranh giới JTAG lại quan trọng

Giá trị của công nghệ quét ranh giới vượt ra ngoài phạm vi kiểm tra cơ bản. Tại Flynn Systems, chúng tôi đã chứng kiến tác động mang tính đột phá của nó đối với việc phát triển và sản xuất PCB. Dưới đây là lý do tại sao nó rất cần thiết:

Phạm vi bao phủ lỗi cao: Phát hiện và chẩn đoán lỗi xuống đến cấp độ chân, đảm bảo không có lỗi nào bị bỏ sót.

Lập trình trong hệ thống: Lập trình các thiết bị như CPLD và bộ nhớ flash trực tiếp trên bo mạch, tiết kiệm thời gian và giảm thiểu lỗi.

Khả năng mở rộng: Thích ứng với sự phức tạp của các thiết kế hiện đại, từ nguyên mẫu đơn giản đến bo mạch sản xuất mật độ cao.

Hiệu quả về chi phí: Giảm nhu cầu về thiết bị kiểm tra chuyên dụng và thiết lập phần cứng đắt tiền.

Hiệu quả: Tinh giản quy trình làm việc và đẩy nhanh thời gian đưa sản phẩm ra thị trường với các giải pháp tự động.