Giao thoa miền xung nhịp trong FPGA

Trong bài viết này, chúng tôi mô tả cách truyền từng tín hiệu riêng lẻ từ miền đồng hồ này sang miền đồng hồ khác.

Xử lý lỗi thời gian và siêu ổn định

Việc chuyển đổi miền xung nhịp (clock domain) bên trong FPGA là một nhiệm vụ phổ biến, nhưng lại là vấn đề mà nhiều nhà thiết kế kỹ thuật số gặp phải. Vấn đề có thể xảy ra nếu nhà thiết kế kỹ thuật số không hiểu rõ tất cả các chi tiết liên quan đến việc chuyển đổi từ miền xung nhịp này sang miền xung nhịp khác. Một miền xung nhịp đơn bao gồm tất cả các Flip-Flop được điều khiển bởi một miền xung nhịp. Trong bài viết này, chúng tôi sẽ mô tả cách truyền từng tín hiệu riêng lẻ từ miền xung nhịp này sang miền xung nhịp khác.

Chuyển từ miền đồng hồ chậm hơn sang miền đồng hồ nhanh hơn

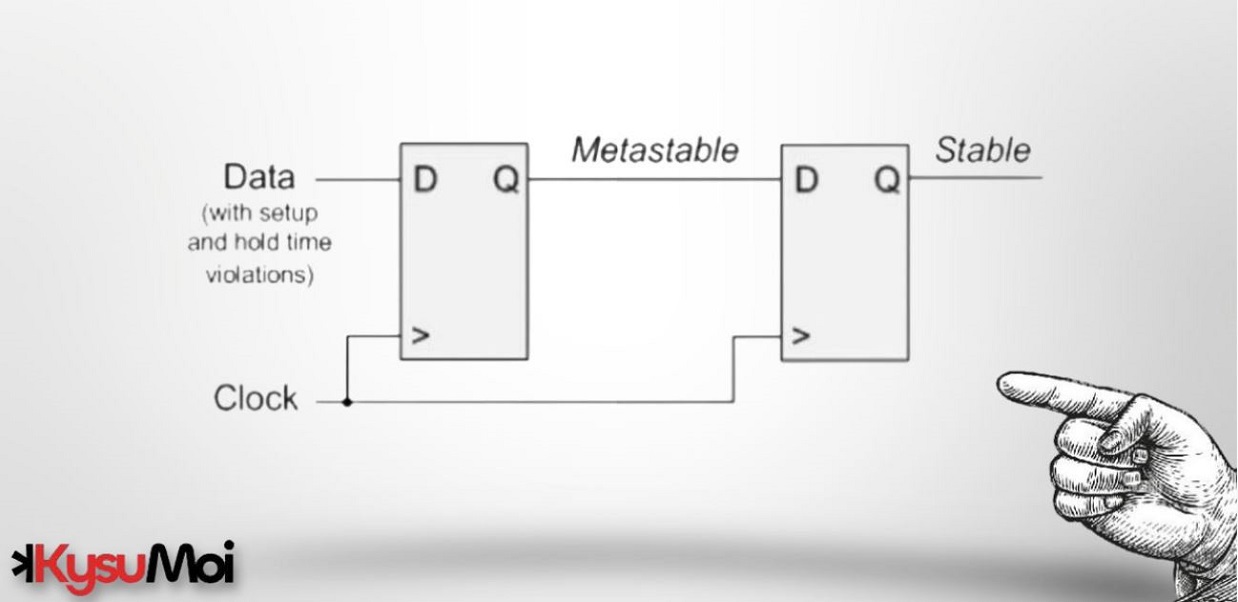

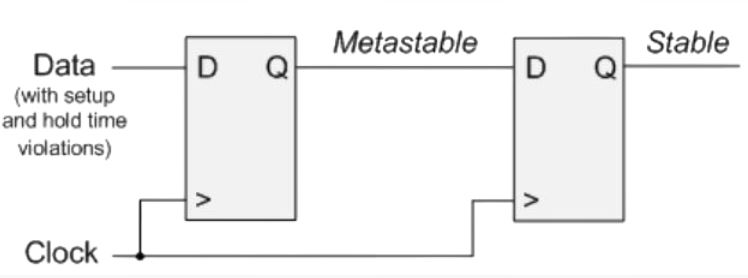

Kiểu giao thoa đơn giản nhất là chuyển từ một miền xung nhịp sang một miền xung nhịp nhanh hơn. Trong kiểu giao thoa này, bạn vẫn phải chịu Metastability. Tất cả những gì bạn cần làm là "double-flop" dữ liệu, được hiển thị trong hình bên dưới.

Đồng hồ chậm hơn là miền đồng hồ nguồn của bạn. Đồng hồ nhanh hơn là miền đồng hồ đích của bạn. Trong miền đồng hồ nhanh hơn, Flip-Flop đầu tiên có đầu ra siêu ổn định. Lý do điều này xảy ra là khi thực hiện phép giao này, sẽ có sự vi phạm thời gian thiết lập và thời gian giữ , là nguyên nhân gây ra siêu ổn định. Chúng ta có thể giải quyết vấn đề này bằng cách chỉ cần đăng ký lại hoặc double-flop dữ liệu trong miền đồng hồ nhanh hơn như minh họa trong hình trên. Đầu ra của Flip-Flop thứ hai sẽ ổn định và bây giờ dữ liệu có thể được sử dụng trong miền đồng hồ nhanh hơn.

Cách tìm kiếm các cạnh khi giao nhau giữa các miền đồng hồ

Đoạn mã dưới đây cho thấy cách bạn có thể tìm kiếm cạnh tăng trên tín hiệu khi chuyển từ miền xung nhịp chậm sang miền xung nhịp nhanh. Lưu ý rằng logic phát hiện cạnh của bạn phải được thực hiện trong miền xung nhịp nhanh.

-- VHDL Example

process (i_Fast_Clk) is

begin

if rising_edge(i_Fast_Clk) then

-- r1_Data is METASTABLE, r2_Data and r3_Data are STABLE

r1_Data <= i_Slow_Data;

r2_Data <= r1_Data;

r3_Data <= r2_Data;

if r3_Data = '0' and r2_Data = '1' then

-- Positive Edge Condition

end if;

end if;

end process;

// Verilog Example:

always @(posedge i_Fast_Clock)

begin

// r1_Data is METASTABLE, r2_Data and r3_Data are STABLE

r1_Data <= i_Slow_Data;

r2_Data <= r1_Data;

r3_Data <= r2_Data;

if (r3_Data == 1'b0 && r2_Data == 1'b1)

begin

// Positive Edge Condition

end

endChuyển từ miền đồng hồ nhanh hơn sang miền đồng hồ chậm hơn

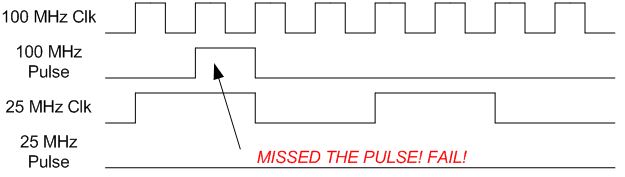

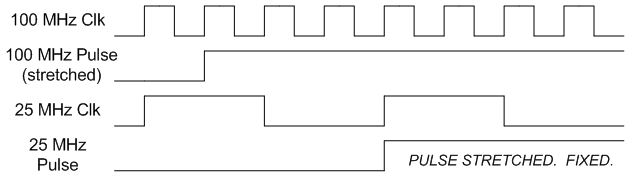

Tình huống này phức tạp hơn một chút so với tình huống trước. Ở đây, chúng ta đang chuyển từ miền xung nhịp nhanh sang miền xung nhịp chậm hơn. Trong tình huống này, thật dễ dàng để hình dung ra một ví dụ trong đó dữ liệu bên trong miền xung nhịp nhanh có thể thay đổi trước khi miền xung nhịp chậm nhìn thấy nó. Ví dụ, hãy xem xét một xung xảy ra trong 1 chu kỳ xung nhịp trong miền xung nhịp 100 MHz, mà bạn đang cố gắng lấy mẫu trong miền xung nhịp 25 MHz. Có khả năng cao là bạn sẽ không bao giờ nhìn thấy xung này nếu bạn chỉ lấy mẫu dữ liệu bằng miền xung nhịp 25 MHz của mình! Để truyền tín hiệu từ miền xung nhịp nhanh sang miền xung nhịp chậm, bạn phải kéo dài tín hiệu của mình . Tham khảo các hình bên dưới để có hình ảnh trực quan về điều này.

Việc kéo giãn dữ liệu xảy ra khi bạn kéo giãn một xung hoặc dữ liệu đủ lâu để đảm bảo miền xung nhịp chậm có cơ hội lấy mẫu. Trong ví dụ trên, bạn cần kéo giãn dữ liệu để đảm bảo thời gian thiết lập và thời gian giữ được đáp ứng bất kể dữ liệu được lấy mẫu khi nào. Để đảm bảo thời gian thiết lập và thời gian giữ được đáp ứng, tôi khuyên bạn nên kéo giãn các xung sao cho chúng mất ít nhất 2 chu kỳ xung nhịp trong miền xung nhịp chậm. Vì vậy, trong ví dụ trên, bạn nên kéo giãn xung 100 MHz thành ít nhất 8 chu kỳ xung nhịp (bạn luôn có thể kéo dài hơn).

Lỗi thời gian và miền đồng hồ giao nhau

Thông thường khi bạn vượt qua miền đồng hồ, bạn sẽ gặp lỗi thời gian. Điều này là bình thường! Đây là các công cụ cho bạn biết rằng bạn sẽ có một tình huống mà thời gian thiết lập và giữ của bạn sẽ không giữ được và bạn sẽ có một điều kiện siêu ổn định. Như tôi đã mô tả trước đó, siêu ổn định là phổ biến cho công việc này, vì vậy miễn là bạn hiểu nó và có thể thiết kế xung quanh nó, bạn sẽ ổn. Bạn nên tìm hiểu cách tạo các ràng buộc thời gian để nới lỏng các công cụ và cho chúng biết rằng bạn là một nhà thiết kế có năng lực và bạn hiểu rằng thiết kế của bạn có thể siêu ổn định. Bạn nên luôn đặt mục tiêu không có lỗi thời gian trong thiết kế của mình. Chính xác cách tạo các ràng buộc thời gian này nằm ngoài phạm vi của bài viết này. Tham khảo hướng dẫn sử dụng của nhà cung cấp FPGA của bạn để biết chi tiết về điều này. Đây là tài liệu tham khảo cho Xilinx và cho Altera . Tôi sẽ cảnh báo bạn, nếu đây là lần đầu tiên bạn xem xét các ràng buộc thời gian, ban đầu bạn sẽ bối rối và choáng ngợp!

Tóm lại, với tư cách là một nhà thiết kế FPGA, bạn sẽ gặp phải những tình huống giao thoa giữa các miền xung nhịp. Bạn cần hiểu rõ những cạm bẫy thường gặp trong những tình huống này. Nếu việc giao thoa đủ đơn giản, bạn có thể chỉ cần double-flop dữ liệu hoặc thực hiện kéo dài xung. Trong phần lớn các trường hợp, bạn có thể cần sử dụng FIFO hỗ trợ hai xung nhịp, một để đọc và một để ghi. Khi cấu trúc mã miền xung nhịp, hãy hết sức cẩn thận để không trộn lẫn các tín hiệu từ cả hai miền xung nhịp.