Phân tích thời gian tĩnh: Đi sâu hơn

Bài viết này giúp người đọc hiểu và đánh giá cao nghệ thuật định thời gian trong mạch kỹ thuật số.

Nhiều bài viết mô tả các kiểm tra ràng buộc liên quan đến STA (kiểm tra thiết lập, kiểm tra giữ, độ rộng xung tối thiểu, v.v.). Tôi tập trung hơn vào việc giải thích bản chất thực sự của STA , cách thức và thời điểm thực hiện trong quá trình thiết kế chip.

Mạch kỹ thuật số chức năng là mạch mà dữ liệu đến và được thu thập đúng thời điểm mong muốn. Kỹ thuật xác thực thời gian của tín hiệu bằng cách phân tích tất cả các đường dẫn khả thi một cách toàn diện, không phụ thuộc vào các vectơ kiểm tra đầu vào của mạch kỹ thuật số được gọi là Phân tích Thời gian Tĩnh (STA).

STA xác định tất cả các lỗi thời gian trong thiết kế. STA kiểm tra xem mạch có thể hoạt động ở tần số xung nhịp mong muốn hay tốc độ định mức hay không. STA chứng minh được nhiều ưu điểm khi so sánh với các phương pháp mô phỏng khác để xác thực thời gian. Tôi xin chia sẻ một số đặc điểm của STA.

- Việc phân tích được thực hiện tĩnh mà không phụ thuộc vào kích thích đầu vào, do đó giúp phân tích nhanh hơn tất cả các đường dẫn thời gian của mạch kỹ thuật số phức tạp chứa 10–100 triệu cổng và tạo báo cáo thời gian ngay lập tức.

- Nó xem xét các điều kiện xấu nhất tương ứng với các đường dẫn thời gian. Nó tính đến độ trễ liên quan đến các cell và mạng lưới cùng với chu kỳ xung nhịp , thời gian đến của tín hiệu và thời gian đến cần thiết làm đầu vào để xác thực các ràng buộc.

- Đôi khi STA được coi là bi quan vì nó xem xét thời gian truyền và chuyển tiếp tệ nhất , khiến các nhà thiết kế vật lý phải có một khoảng thời gian nhất định để xác thực mạch.

- Công cụ STA tính toán S lack = Thời gian đến yêu cầu (RAT) - Thời gian đến thực tế (AAT), bằng cách theo dõi tất cả các đường dẫn quan trọng chịu trách nhiệm cho các vi phạm thời gian.

- STA là trụ cột chính trong “ đóng thời gian ”, một trong những bước trong thiết kế vật lý. Việc tối ưu hóa thời gian được thực hiện cho mạch dựa trên báo cáo thời gian do công cụ STA tạo ra. Các đường dẫn được cho là đáp ứng thời gian khi nó có độ chùng dương và thiết kế có thời gian đóng .

- STA không xác minh chức năng của mạch số, do đó chỉ những mạch hợp lệ về mặt logic hoặc chức năng mới được đưa vào làm đầu vào. Nếu không, quá trình phân tích sẽ phức tạp và đưa ra kết quả không chính xác.

- Về lý tưởng, STA thực hiện các phép tính bằng cách xem xét một chu kỳ xung nhịp. Môi trường thực hiện STA phải được xác định chính xác để phân tích chính xác tất cả các vi phạm thời gian. Nó phải bao gồm việc xác định các xung nhịp (chu kỳ, nguồn xung nhịp, chu kỳ làm việc, độ lệch, v.v.), điều kiện hoạt động ( PVT: Trường hợp tốt nhất, điển hình và xấu nhất), nhiều miền xung nhịp , thời gian IO, đường dẫn xung nhịp có cổng , sai, không đồng bộ và đa chu kỳ.

- STA chỉ chứng minh được kết quả chính xác khi các đường dẫn được coi là " đúng ". Không phải tất cả các đường dẫn trong một mạch đều là đường dẫn đúng về mặt logic. Có thể có các đường dẫn sai và đường dẫn nhiều chu kỳ trong mạch. Các đường dẫn sai về mặt logic hoặc các đường dẫn không truyền bất kỳ dữ liệu nào được gọi là đường dẫn sai, trong khi các đường dẫn mất hơn một chu kỳ xung nhịp để truyền tín hiệu là các đường dẫn nhiều chu kỳ. STA không biết đường dẫn nào không đúng, do đó, các nhà thiết kế phải chỉ rõ cho STA đường dẫn nào sai và đường dẫn nào nhiều chu kỳ để có được dữ liệu thời gian chính xác.

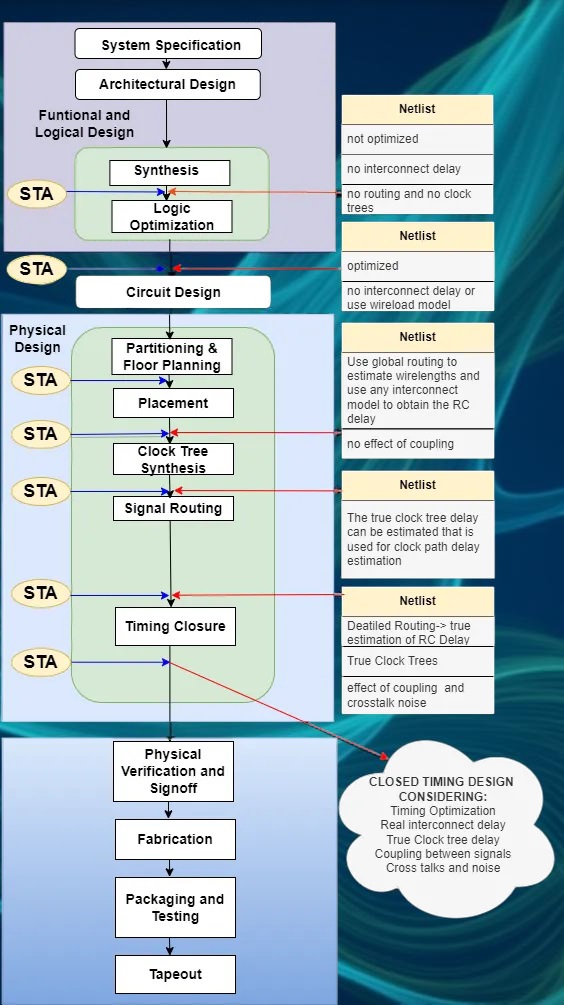

KHI NÀO STA ĐƯỢC THỰC HIỆN TRONG LUỒNG THIẾT KẾ?

Liệu nó chỉ được thực hiện trong quá trình đóng thời gian của quy trình thiết kế vật lý? Không hẳn vậy! Thời gian được xác minh ở tất cả các giai đoạn thiết kế hoặc các cấp độ trừu tượng trong luồng thiết kế. Không phải tất cả thông tin cần thiết để ước tính độ trễ đều có sẵn ở các giai đoạn thiết kế trước đó. Vì vậy, STA được thực hiện sau mỗi cấp độ để xác thực thời gian và tìm ra các đường dẫn quan trọng gây ra vi phạm. Tôi đã tạo một hình ảnh chi tiết về luồng thiết kế mạch VLSI và vị trí thực hiện STA, dựa trên đặc tả netlist.

- Trong thiết kế RTL , thông tin thời gian cần thiết không có sẵn; chức năng của mạch được xác minh ở giai đoạn này.

- Sau khi netlist cấp cổng được tổng hợp từ thiết kế RTL, STA được thực hiện. Ở đây, chúng ta có ít nhất thông tin về độ trễ của cell, thời gian liên quan đến flip-flop và các cell tiêu chuẩn như lan truyền , và độ trễ nhiễm bẩn , bao gồm cả chu kỳ xung nhịp. Vì vậy, có thể thực hiện các kiểm tra thiết lập và giữ cơ bản.

- Trước khi tối ưu hóa logic , STA được thực hiện để xác định các đường dẫn quan trọng và độ trễ xấu nhất hoặc độ trễ tổng thể .

- Sau khi tối ưu hóa logic, STA được thực hiện để tìm bất kỳ vi phạm thời gian nào ngay cả sau khi thực hiện tối ưu hóa mạch.

- Cho đến thời điểm này, độ trễ ròng được coi là bằng không hoặc có thể xem xét mô hình tải trọng dây để ước tính độ trễ ròng ở một mức độ nhất định.

- Việc triển khai vật lý thực sự của các mạch kỹ thuật số, các cell, mô-đun, macro tiêu chuẩn, v.v., được kết nối với nhau bằng các đường kim loại . Các kết nối kim loại này góp phần gây ra độ trễ kết nối (độ trễ điện trở và tụ điện: độ trễ RC ), một mối quan tâm lớn trong các công nghệ siêu nhỏ. Điều này phụ thuộc vào nhiều yếu tố trong thiết kế vật lý, trong đó một số yếu tố bao gồm chiều dài dây dẫn, loại định tuyến, hệ số quan trọng của lưới, vị trí đặt cell và mô-đun, cũng như mô hình kết nối được sử dụng.

- Trước khi định tuyến tín hiệu, độ trễ kết nối có thể được ước tính gần đúng từ định tuyến toàn cầu, tuy nhiên vì không có thông tin định tuyến chi tiết nên không thể xác định được hiệu ứng ghép nối của các tín hiệu gần nhau.

- Hơn nữa, cho đến thời điểm này, các nguồn xung nhịp được coi là lý tưởng và không có độ lệch xung nhịp/biến thiên thời gian nào được xem xét. Sau khi tổng hợp cây xung nhịp trong thiết kế vật lý, ước tính thực sự về độ trễ đường truyền xung nhịp có thể được tìm thấy. STA được thực hiện có tính đến các biến thiên không gian và thời gian của tín hiệu xung nhịp.

- Độ trễ RC thực tế chỉ có thể thu được sau khi định tuyến chi tiết được thực hiện. Công cụ trích xuất được sử dụng để trích xuất các giá trị RC ký sinh chi tiết từ thiết kế mạch định tuyến tín hiệu. Đây là một quá trình lặp đi lặp lại, trong đó các giá trị chính xác có thể thu được bằng cách tăng thời gian chạy.

- Cuối cùng, các vấn đề về tính toàn vẹn của tín hiệu như hiệu ứng ghép nối giữa các tín hiệu và nhiễu xuyên âm được mô hình hóa để thực hiện STA.

Sau khi đã biết những điều cần cân nhắc và thời điểm thực hiện STA, chúng ta sẽ tìm hiểu sâu hơn về cách đưa những điều này vào để thực hiện STA.

STA CÓ THỂ CÓ ĐƯỢC THÔNG TIN CẦN THIẾT NHƯ THẾ NÀO?

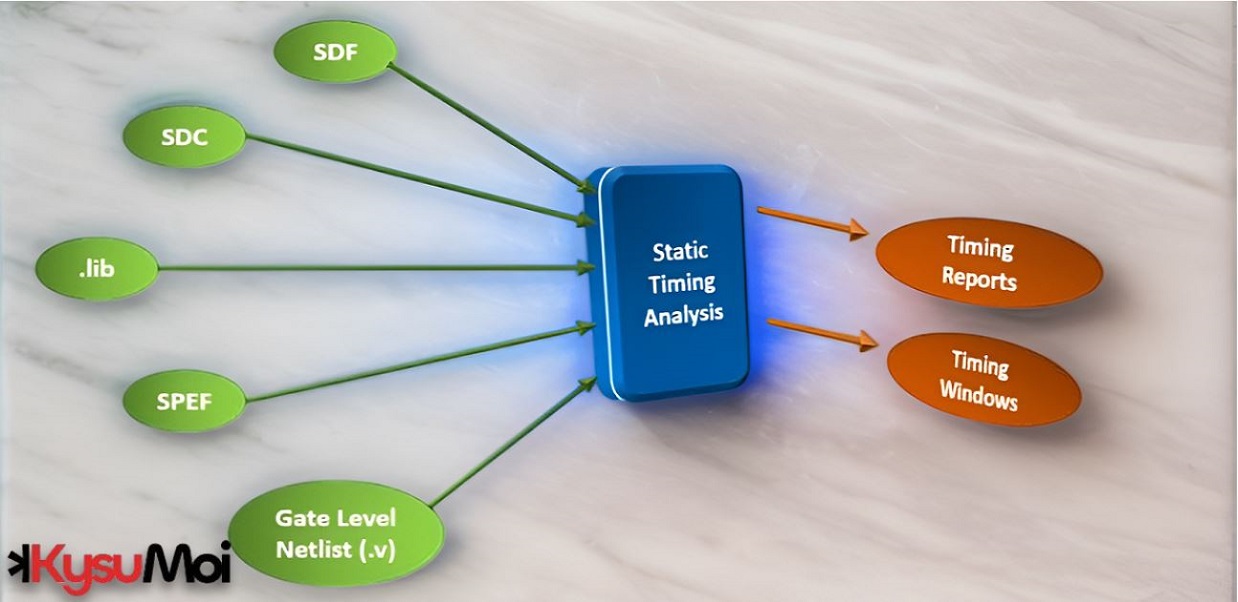

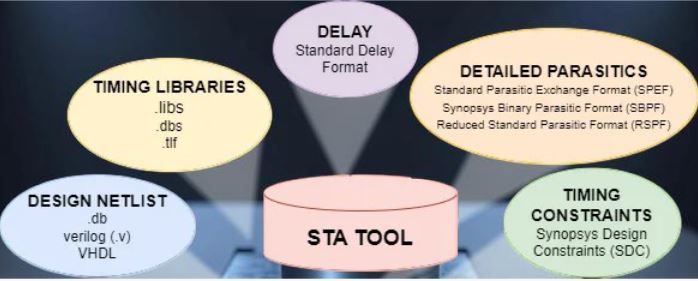

STA thu thập thông tin chi tiết về mạch, môi trường, thông tin thời gian, các ký sinh chi tiết, ràng buộc thời gian và thông tin độ trễ từ nhiều định nghĩa định dạng tệp khác nhau. Dưới đây là thông tin chi tiết về các loại tệp mà STA sử dụng để tạo báo cáo thời gian.

- Thiết kế của mạch, tức là danh sách mạng cấp cổng, được đưa ra dưới dạng văn bản Verilog (.v) hoặc tập lệnh VHDL hoặc dưới dạng tệp thư viện - cơ sở dữ liệu (.db).

- Thư viện thời gian cung cấp thông tin chủ yếu mà STA yêu cầu. Nó thường được cung cấp dưới dạng Tệp Thời gian Tự do (.lib) . Thư viện này định nghĩa nhiều khía cạnh như miền xung nhịp, điều kiện hoạt động, mô hình thời gian, giảm tốc độ xung nhịp, ngưỡng, độ trễ lan truyền, mô hình nhiễu, mô hình tiêu tán công suất, nhiều thuộc tính liên quan đến thư viện cell, ký sinh kết nối, các khía cạnh về tính toàn vẹn tín hiệu như nhiễu xuyên âm và lỗi, môi trường thiết kế như chỉ định xung nhịp, thời gian IO, đường dẫn sai, v.v.

- Thông tin về thời gian và độ trễ của mạch được cung cấp dưới dạng tệp văn bản ASCII chuẩn IEEE, được gọi là Định dạng Độ trễ Chuẩn (SDF) và được tạo ra sau khi biên dịch thiết kế. Tệp này chứa dữ liệu thời gian cho chú thích ngược và chú thích xuôi. Độ trễ của cell, kiểm tra thời gian, sự lan truyền xung, độ trễ kết nối, v.v. là một số chi tiết có trong tệp SDF.

- Giá trị ký sinh chính xác và chi tiết chỉ có thể thu được sau khi đặt và định tuyến tín hiệu. Công cụ trích xuất ký sinh sẽ trích xuất các giá trị R, L và C, đôi khi công cụ đặt và định tuyến cũng thực hiện việc này và được lưu trữ trong Định dạng Trao đổi Ký sinh Chuẩn (SPEF). Có nhiều mô hình khác nhau để biểu diễn ký sinh kết nối . SPEF chủ yếu hỗ trợ mô hình tụ điện tập trung, mô hình mạng phân tán và mô hình mạng giảm . Hơn nữa, ký sinh cũng phụ thuộc vào quy trình: trường hợp tốt nhất, điển hình và trường hợp xấu nhất. Các định dạng tệp khác là SBPF và RSPF.

- Cuối cùng, các ràng buộc về thời gian của thiết kế được đưa ra dưới dạng Ràng buộc Thiết kế Synopsys (SDC). Nó được mở rộng để cung cấp các ràng buộc về công suất và diện tích của thiết kế.

Công cụ STA thu thập thông tin cần thiết liên quan đến thiết kế thông qua các tệp đã đề cập ở trên, xác thực thiết kế, kiểm tra vi phạm thời gian và tạo báo cáo thời gian. Việc đóng thời gian của quy trình thiết kế vật lý sử dụng báo cáo thời gian này để xác định độ trễ: trường hợp xấu nhất hoặc tổng thể và tối ưu hóa nếu có độ trễ âm trong thiết kế. Nó thực hiện 3 tối ưu hóa chính:

- Vị trí truyền động thời gian - giảm độ trễ tín hiệu bằng cách đặt các thành phần mạch

- Định tuyến tín hiệu theo thời gian - giảm độ trễ tín hiệu bằng cách chỉ định tuyến đường và cấu trúc định tuyến.

- Tổng hợp vật lý - cải thiện độ trễ bằng cách sửa đổi danh sách mạng thiết kế.

PHẦN KẾT LUẬN:

STA được sử dụng rộng rãi trong thiết kế chip để xác thực thời gian và hiệu suất của mạch kỹ thuật số. Tuy nhiên, nó có một số nhược điểm : không xác minh được chức năng logic của mạch, không xử lý được các trạng thái trở kháng cao, không kiểm tra xem các bộ đồng bộ hóa có được sử dụng đúng giữa các miền xung nhịp bất đồng bộ khác nhau hay không, cần phải cẩn thận tại giao diện giữa miền analog và miền kỹ thuật số (vì STA không xử lý được các khối analog), xử lý các đường dẫn sai và nhiều vấn đề khác. Đôi khi, trong một thiết kế rất phức tạp, các đường dẫn có thể không nhạy. Do đó, STA khó có thể thay thế các công cụ mô phỏng truyền thống.

Quan trọng hơn, STA truyền thống không có khả năng chống chịu các biến đổi quy trình phát sinh do môi trường, nguồn điện, nhiệt độ, lão hóa, v.v. Biến đổi quy trình làm cho việc phân tích trở nên phức tạp và phức tạp hơn vì nó rất ngẫu nhiên. Để xử lý các biến đổi quy trình, độ trễ cổng và độ trễ ròng được mô hình hóa bằng các biến đổi ngẫu nhiên và được biểu diễn dưới dạng phân phối xác suất . Ví dụ, mô hình phân phối độ trễ được sử dụng rộng rãi nhất là phân phối chuẩn hoặc phân phối Gauss. Lớp tổng quát hóa này của STA được gọi là STA Thống kê (SSTA), ngày càng phổ biến trong các thiết kế tiên tiến do sự tồn tại của các biến đổi trong các nút công nghệ dưới micron.