Phân vùng SoC và thực thi thành công

Hướng dẫn toàn diện về việc phân vùng và thực thi thành công chip SoC.

Thiết kế Hệ thống trên Chip (SoC) là một quy trình phức tạp bao gồm nhiều mô-đun chức năng, mỗi mô-đun có các yêu cầu riêng. Phân vùng là một phương pháp quan trọng được sử dụng để quản lý tính phức tạp bằng cách chia SoC thành các khối dễ quản lý và gắn kết. Quy trình này ảnh hưởng đến hiệu quả thiết kế, hiệu suất và khả năng sản xuất.

Phân vùng logic

Phân vùng logic là việc phân đoạn thiết kế SoC dựa trên ranh giới chức năng và logic. Điều này đảm bảo các chức năng riêng biệt được đóng gói trong các mô-đun hoặc hệ thống con được xác định.

Thực hành tốt nhất

- Phân tích chức năng: Xác định các chức năng cốt lõi và phân bổ chúng vào các phân vùng cụ thể.

- Định nghĩa giao diện: Xác định rõ ràng các giao thức truyền thông và cơ chế trao đổi dữ liệu giữa các phân vùng.

- Tối ưu hóa hệ thống phân cấp: Thiết lập hệ thống phân cấp giúp giảm thiểu sự phụ thuộc lẫn nhau và tối đa hóa tính mô-đun.

Phân vùng vật lý

Phân vùng vật lý bao gồm việc chia bố cục SoC thành các vùng hoặc khối vật lý trên chip. Giai đoạn này tập trung vào việc sắp xếp, định tuyến và đạt được các mục tiêu thiết kế vật lý như đóng thời gian và hiệu suất năng lượng.

Thực hành tốt nhất

- Quy hoạch mặt bằng: Phát triển bố cục tối ưu để cân bằng hiệu suất, công suất và diện tích (PPA).

- Vị trí cụm: Nhóm logic liên quan về mặt vật lý để có lợi ích về thời gian và công suất.

- Chiến lược định tuyến: Giảm thiểu chiều dài dây và quản lý tắc nghẽn hiệu quả.

Mô-đun lặp lại: Xác định các mô-đun logic có thể lặp lại. Nếu một mô-đun có thể lặp lại, việc phân vùng vật lý sẽ mang lại những lợi thế to lớn, chẳng hạn như thực hiện lệnh đặt và định tuyến một lần và đóng dấu N lần. Cách tiếp cận này đặc biệt hữu ích trong quá trình sửa lỗi lệnh thay đổi kỹ thuật quan trọng (ECO) ở giai đoạn băng tải.

Cân nhắc về diện tích: Đảm bảo việc phân vùng một mô-đun không gây ra chi phí diện tích đáng kể. Nếu phân vùng gây ra thêm một vấn đề về diện tích, thì nó không phải là ứng cử viên phù hợp để phân vùng.

Phân vùng logic so với phân vùng vật lý

Sự phụ thuộc lẫn nhau và sự đánh đổi

Phân vùng logic quyết định các ràng buộc về bố cục vật lý, trong khi tính khả thi về mặt vật lý có thể đòi hỏi phải điều chỉnh ranh giới logic. Việc cân nhắc cả hai yếu tố này là rất quan trọng.

Tầm quan trọng của phân vùng trong thiết kế SoC

Lợi ích của việc phân vùng hiệu quả

- Khả năng quản lý thiết kế được cải thiện: Đơn giản hóa các thiết kế SoC phức tạp thành các đơn vị nhỏ hơn, dễ quản lý hơn.

- Phát triển song song: Cho phép làm việc đồng thời giữa các nhóm.

- Gỡ lỗi nâng cao: Tạo điều kiện cho các nỗ lực xác minh và gỡ lỗi có mục tiêu.

- Thiết kế tái sử dụng: Thúc đẩy tái sử dụng IP trong các dự án.

Những thách thức của việc phân vùng kém

- Độ phức tạp tăng cao: Phân vùng được định nghĩa không rõ ràng có thể dẫn đến các vấn đề phụ thuộc lẫn nhau. Ví dụ: Nhà thiết kế có thể chọn thêm một thanh ghi, điều này có thể dẫn đến một cổng mới tại ranh giới phân vùng — Điều này làm gián đoạn thiết kế vật lý.

- Nút thắt thời gian: Phân vùng không tối ưu có thể dẫn đến vi phạm thời gian, thời gian chạy dài, bỏ lỡ kiểm tra thời gian.

Điểm đóng băng phân vùng

Khi nào nên đóng băng một phân vùng

- Phân vùng logic: Đóng băng sau khi xác thực chức năng và phê duyệt RTL.

- Phân vùng vật lý: Đóng băng quá trình lập kế hoạch mặt bằng và tối ưu hóa vị trí ban đầu.

Những gì cần đóng băng trong phân vùng logic và vật lý

- Phân vùng logic: Giao diện, giao thức truyền thông và ranh giới chức năng.

- Phân vùng vật lý: Sơ đồ mặt bằng, vị trí khối nhà và các tuyến đường định tuyến quan trọng.

Các nghiên cứu điển hình và ví dụ thực tế

Kịch bản thành công 1: SoC di động

Bối cảnh : SoC di động tích hợp CPU, GPU, modem, DSP và các hệ thống con I/O vào một khuôn duy nhất, hướng đến hiệu suất cao và mức tiêu thụ điện năng thấp cho điện thoại thông minh.

Chiến lược phân vùng :

- Nhóm thiết kế phân vùng SoC thành các miền năng lượng (ví dụ: lõi CPU trong một miền, GPU trong miền khác, modem trong miền thứ ba) để cho phép quản lý năng lượng độc lập.

- Các giao diện tốc độ cao (ví dụ: PCIe, USB) được tách biệt về mặt vật lý khỏi các khối tính toán để giảm nhiễu và tối ưu hóa tính toàn vẹn của tín hiệu.

Thành công :

- Hiệu suất năng lượng : Công nghệ điều chỉnh điện áp và tần số động (DVFS) hoạt động liền mạch trên các phân vùng, giúp giảm mức tiêu thụ điện năng tới 30% trong điều kiện nhàn rỗi hoặc tải thấp.

- Quản lý nhiệt : Việc tách biệt vật lý các khối sinh nhiệt (CPU/GPU) cho phép tản nhiệt tốt hơn, tránh hiện tượng giảm hiệu năng do nhiệt.

- Thời gian đưa ra thị trường nhanh hơn : Ranh giới phân vùng rõ ràng cho phép nhiều nhóm phát triển song song (ví dụ: nhóm CPU, nhóm GPU).

Bài học kinh nghiệm :

- Việc xác định sớm các miền năng lượng và giao thức giao diện là chìa khóa để tránh các vấn đề về tích hợp.

- Nên tránh phân vùng quá mức — quá nhiều khối nhỏ có thể làm tăng độ phức tạp của quá trình định tuyến và diện tích khuôn.

Tình huống nguy hiểm 1: Phân vùng quá mức trong SoC ô tô

Bối cảnh : Một SoC ô tô được thiết kế cho các hệ thống hỗ trợ người lái tiên tiến (ADAS) yêu cầu xử lý thời gian thực, dự phòng quan trọng đối với an toàn và độ trễ thấp.

Chiến lược phân vùng :

- Nhóm đã tích cực phân chia thiết kế thành nhiều khối nhỏ (ví dụ: phân vùng riêng cho từng giao diện cảm biến, bộ xử lý và bộ điều khiển bộ nhớ) để tối đa hóa tính mô-đun và khả năng tái sử dụng.

Cạm bẫy :

- Chi phí kết nối : Số lượng phân vùng quá nhiều dẫn đến kết nối trên chip (NoC) phình to, làm tăng độ trễ thêm 15% và tiêu tốn thêm 20% diện tích khuôn so với kế hoạch.

- Sự cố đóng thời gian : Việc định tuyến tín hiệu giữa các phân vùng trở thành nút thắt, gây ra sự chậm trễ trong việc đáp ứng các yêu cầu về thời gian.

- Thách thức xác minh : Sự phức tạp của việc tích hợp quá nhiều phân vùng đã làm nhóm xác minh quá tải, khiến việc phát hành băng bị chậm lại ba tháng.

Bài học kinh nghiệm :

- Cân bằng giữa tính mô-đun và tính thực tế — ít phân vùng hơn, lớn hơn có thể đơn giản hóa việc định tuyến và xác minh.

- Mô phỏng hiệu suất kết nối ngay từ giai đoạn thiết kế để phát hiện các vấn đề về độ trễ và diện tích.

- Việc phân vùng quá mức để tái sử dụng trong tương lai sẽ rất rủi ro nếu mốc thời gian của dự án hiện tại và mục tiêu PPA bị ảnh hưởng.

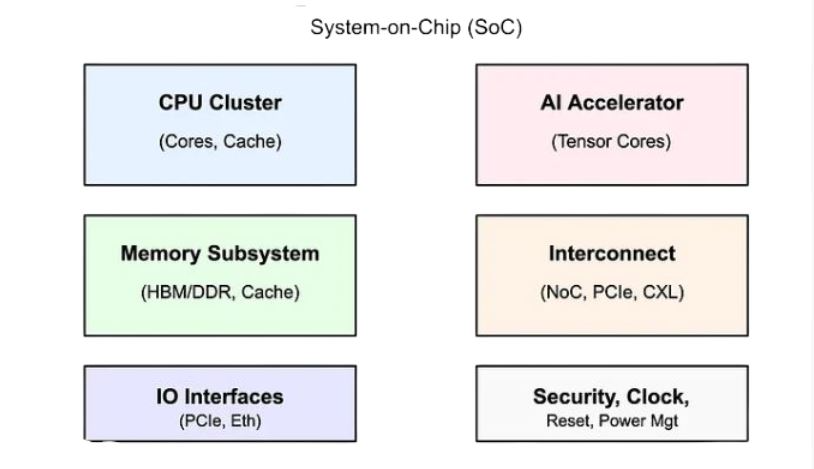

Kịch bản thành công 2: AI Accelerator

Bối cảnh : Một SoC AI được thiết kế cho khối lượng công việc học máy cần có các đơn vị tính toán song song lớn, bộ nhớ băng thông cao (HBM) và kết nối nhanh.

Chiến lược phân vùng :

- Thiết kế được phân chia thành các cụm tính toán (ví dụ: lõi xử lý), bộ điều khiển bộ nhớ và khối I/O.

- Các cụm tính toán được sao chép đối xứng trên toàn bộ khuôn, trong khi các giao diện HBM được đặt gần các cạnh để đảm bảo tính toàn vẹn của tín hiệu tối ưu.

Thành công :

- Khả năng mở rộng : Các phân vùng tính toán theo mô-đun cho phép mở rộng dễ dàng (ví dụ: tăng gấp đôi số lõi ở thế hệ tiếp theo) mà không cần thiết kế lại toàn bộ chip.

- Tối ưu hóa băng thông : Đặt bộ điều khiển bộ nhớ gần HBM giúp giảm độ trễ và tăng thông lượng lên 40% so với thiết kế bộ nhớ tập trung.

- Cải thiện năng suất : Phân vùng cho phép cô lập lỗi — các cụm tính toán bị lỗi có thể bị vô hiệu hóa, cứu vãn các khuôn hoạt động một phần.

Bài học kinh nghiệm :

- Tính đối xứng trong phân vùng có thể đơn giản hóa bố cục và cải thiện khả năng sản xuất.

- Sự gần gũi của các giao diện tốc độ cao với các kết nối bên ngoài là rất quan trọng đối với hiệu suất.

- Thiết kế để thử nghiệm (DFT) và tính dự phòng nên được tích hợp vào các phân vùng để tối đa hóa năng suất.

Tình huống nguy hiểm 2: SoC tín hiệu hỗn hợp (ví dụ: Thiết bị IoT)

Bối cảnh : Một IoT SoC kết hợp logic kỹ thuật số (vi điều khiển, ngăn xếp không dây) với các thành phần tương tự (bộ thu phát RF, ADC) trên một khuôn duy nhất.

Chiến lược phân vùng :

- Ban đầu, nhóm nghiên cứu đặt các khối kỹ thuật số và khối tương tự gần nhau để giảm thiểu diện tích khuôn, cho rằng các vòng bảo vệ và lớp chắn sẽ làm giảm tiếng ồn.

Cạm bẫy :

- Ghép nối nhiễu : Nhiễu chuyển mạch kỹ thuật số bị rò rỉ vào khối RF tương tự, làm giảm tỷ lệ tín hiệu trên nhiễu (SNR) xuống 10 dB và khiến phạm vi không dây giảm 25%.

- Chi phí làm lại : Thiết kế lại ở giai đoạn cuối để tách biệt vật lý các phân vùng tương tự và kỹ thuật số làm tăng thêm sáu tháng so với tiến độ và làm tăng chi phí thêm 15%.

- Các vấn đề về phân phối điện : Việc lập kế hoạch phân tách lưới điện không đầy đủ đã dẫn đến tình trạng sụt giảm điện áp ở phần analog trong thời gian hoạt động kỹ thuật số cao điểm.

Bài học kinh nghiệm :

- Sự tách biệt vật lý giữa miền tương tự và miền kỹ thuật số là không thể thương lượng — ưu tiên sự cô lập hơn là tiết kiệm diện tích.

- Mô hình hóa nhiễu và phân phối công suất trên các phân vùng sớm bằng cách sử dụng các công cụ mô phỏng tín hiệu hỗn hợp.

- Phân bổ vùng đệm hoặc không gian trống giữa các khối nhạy cảm để đảm bảo thiết kế có thể sử dụng trong tương lai.

Xu hướng phân vùng SoC

Phân vùng thiết kế vật lý trong phát triển Hệ thống trên chip (SoC) bao gồm việc chia bố cục chip thành các vùng vật lý riêng biệt để tối ưu hóa vị trí đặt, định tuyến, phân phối điện năng và năng suất sản xuất. Các phương pháp mới nổi như phân vùng dựa trên AI, thiết kế IC 3D tiên tiến và liên kết lai đang chuyển đổi quy trình này. Dưới đây, tôi sẽ tìm hiểu cách mỗi phương pháp tác động đến các quyết định phân vùng vật lý trong giai đoạn thiết kế back-end.

Phân vùng vật lý do AI điều khiển

AI đang được tích hợp vào các công cụ thiết kế vật lý để tự động hóa và tối ưu hóa việc phân vùng bố cục của chip thành các khối vật lý, nâng cao hiệu quả bố trí và quy hoạch mặt bằng.

Cách thức hoạt động :

- Đầu vào : Các mô hình AI sử dụng danh sách mạng, ràng buộc thời gian, ngân sách năng lượng và dữ liệu nút quy trình (ví dụ: quy tắc thiết kế 5nm) để đề xuất ranh giới khối vật lý.

- Phân tích : Thuật toán dự đoán tình trạng tắc nghẽn, chiều dài dây và nhu cầu lưới điện, đề xuất phân vùng giúp giảm thiểu độ phức tạp của định tuyến hoặc tình trạng mất IR.

- Thực hiện : AI lặp lại sơ đồ mặt bằng, điều chỉnh hình dạng khối và vị trí chân cắm — ví dụ: nhóm logic tốc độ cao gần các bàn phím I/O để giảm độ trễ tín hiệu.

Thuận lợi :

- Giảm tắc nghẽn : Trong SoC phức tạp, AI có thể phân chia một khối logic dày đặc thành hai vùng nhỏ hơn, cắt giảm tắc nghẽn định tuyến xuống 15% và giảm thời gian đóng.

- Tối ưu hóa năng lượng : AI có thể nhóm các mô-đun công suất thấp thành một phân vùng duy nhất, giúp giảm diện tích lưới điện xuống 10%.

- Tự động hóa : Thời gian lập kế hoạch mặt bằng giảm từ vài tuần xuống còn vài ngày vì AI đánh giá hàng nghìn bố cục theo các mục tiêu PPA (công suất, hiệu suất, diện tích).

Thách thức :

- Độ chính xác : AI dựa vào dữ liệu đào tạo; nếu không có bố cục trước cho một nút quy trình mới, các dự đoán có thể bỏ sót các hiệu ứng vật lý tinh tế như điểm nóng quang khắc.

- Tích hợp : Các công cụ EDA hiện tại (ví dụ: luồng đặt và định tuyến) có thể không hỗ trợ đầy đủ các phân vùng do AI điều khiển, cần phải điều chỉnh thủ công.

- Chi phí chung : Việc tinh chỉnh các đề xuất AI có thể làm tăng thêm độ phức tạp nếu phân vùng ban đầu không khớp với các bước tiếp theo như tổng hợp cây đồng hồ.

Tác động đến phân vùng vật lý :

- AI chuyển đổi phân vùng vật lý từ phương pháp thử và sai thủ công sang tối ưu hóa dự đoán. Ví dụ, trong SoC di động, nó có thể tạo ra một phân vùng hình chữ nhật cho GPU gần cạnh chip, đảm bảo các tuyến đường ngắn hơn đến các chân bộ nhớ ngoài, một quyết định được xác thực bằng các số liệu về chiều dài dây dẫn được giảm bớt.

Thiết kế IC 3D tiên tiến trong phân vùng vật lý

Tổng quan : IC 3D xếp chồng nhiều khuôn theo chiều dọc, sử dụng các lỗ xuyên silicon (TSV) để kết nối các phân vùng vật lý trên nhiều lớp, mở rộng phân vùng vào trục z trong quá trình thiết kế vật lý.

Cách thức hoạt động :

- Chiến lược phân vùng : Các khối vật lý được gán cho các khuôn riêng biệt — ví dụ, logic tính toán trên một lớp, SRAM trên lớp khác — dựa trên vị trí gần và nhu cầu kết nối.

- Cân nhắc về bố cục : TSV được đặt một cách chiến lược trong các vách ngăn để liên kết các lớp, đòi hỏi phải căn chỉnh cẩn thận trong quá trình thiết kế mặt bằng.

- Ví dụ : Trong SoC hiệu suất cao, thiết kế vật lý có thể phân vùng một khối bộ nhớ đệm lớn vào một khuôn trên cùng, ngay phía trên các đơn vị tính toán, với TSV xử lý việc truyền dữ liệu theo chiều dọc.

Thuận lợi :

- Giảm chiều dài dây : Xếp chồng cắt giảm tuyến đường ngang tới 50% vì tín hiệu truyền theo chiều dọc qua TSV thay vì lan rộng trên mặt phẳng 2D.

- Mật độ : SoC tín hiệu hỗn hợp có thể phân chia các khối tương tự thành một khối ở dưới cùng và logic kỹ thuật số ở trên, thu hẹp diện tích 2D đồng thời cô lập các vùng nhạy cảm với nhiễu.

- Năng suất : Phân chia các khối bị lỗi thành nhiều lớp cho phép tận dụng một phần khuôn, cải thiện khả năng sản xuất tổng thể.

Thách thức :

- Tác động nhiệt : Các phân vùng tỏa nhiều nhiệt (ví dụ: lõi CPU) trên các lớp trên cùng có thể làm quá nhiệt các khuôn dưới, làm phức tạp việc bố trí vật lý.

- Chi phí TSV : Mỗi TSV chiếm không gian bố trí (ví dụ: khoảng cách 5–10µm), buộc phải phân vùng lớn hơn hoặc thiết kế thưa hơn để chứa chúng.

- Căn chỉnh : Các TSV không thẳng hàng trong quá trình xếp chồng sẽ làm gián đoạn quá trình định tuyến, đòi hỏi phải lập kế hoạch mặt bằng chính xác trên khắp các khuôn.

Tác động đến phân vùng vật lý :

- IC 3D đòi hỏi một chiến lược phân vùng theo chiều dọc. Các nhà thiết kế có thể tách bộ điều khiển bộ nhớ khỏi khối logic của nó trên hai đế, đặt các mảng TSV ở các cạnh phân vùng để tối ưu hóa đường dẫn tín hiệu, một lựa chọn được thúc đẩy bởi mật độ bố trí và bản đồ nhiệt.

Vai trò của liên kết lai trong phân vùng vật lý

Tổng quan : Liên kết lai kết nối trực tiếp các miếng đệm đồng giữa các khuôn xếp chồng mà không cần TSV, cho phép kết nối bước cực nhỏ (ví dụ: 1µm) và xác định lại độ chi tiết phân vùng vật lý trong các hệ thống nhiều khuôn.

Cách thức hoạt động :

- Quy trình : Các khuôn được liên kết bằng các kết nối đồng với đồng, cho phép các vách ngăn trải dài qua ranh giới khuôn với khoảng cách tối thiểu.

- Ứng dụng phân vùng : Các khối vật lý có thể được chia ở mức độ chi tiết hơn — ví dụ, một phân vùng duy nhất như DSP có thể nằm trên hai khuôn, với các miếng đệm liên kết thay thế các lỗ thông truyền thống.

- Ví dụ : Trong IoT SoC, bố cục vật lý của bộ thu phát RF có thể nằm trên một khuôn, được liên kết trực tiếp với phân vùng kỹ thuật số trên một khuôn khác, tránh các vùng cấm TSV.

Thuận lợi :

- Mật độ kết nối : Với khoảng cách thấp tới 1µm, liên kết lai hỗ trợ nhiều kết nối hơn 10 lần trên mỗi cạnh phân vùng so với TSV, cho phép bố trí chặt chẽ hơn.

- Tính toàn vẹn của tín hiệu : Ký sinh thấp hơn cải thiện thời gian, cho phép phân vùng được đặt gần I/O quan trọng hơn mà không bị suy giảm.

- Tiết kiệm diện tích : Việc loại bỏ TSV giúp giải phóng không gian bố trí, cho phép các nhà thiết kế thu nhỏ các phân vùng hoặc tích hợp nhiều chức năng hơn cho mỗi khuôn.

Thách thức :

- Độ chính xác căn chỉnh : Liên kết đòi hỏi độ chính xác dưới micron, do đó ranh giới phân vùng phải căn chỉnh hoàn hảo trong quá trình thiết kế mặt bằng, tăng công sức thiết kế.

- Liên kết nhiệt : Liên kết trực tiếp truyền nhiệt giữa các vách ngăn hiệu quả hơn, đòi hỏi phải bố trí các điểm nóng cẩn thận.

- Chi phí : Độ chính xác sản xuất cao hạn chế liên kết lai với các thiết kế cao cấp, ảnh hưởng đến phân chia chi phí-lợi ích.

Tác động đến phân vùng vật lý :

- Liên kết lai cho phép phân vùng đa đế liền mạch. Đối với một SoC nặng về tính toán, một khối logic lớn có thể được chia thành hai đế liên kết, với các miếng đệm liên kết được đặt dọc theo cạnh vật lý của phân vùng để duy trì tính liên tục, giảm nhu cầu về các kênh định tuyến rộng.

Những cân nhắc cụ thể về thiết kế vật lý

- Hiệu ứng Synergy trong quy hoạch mặt bằng : AI có thể tối ưu hóa bố cục 3D và liên kết lai bằng cách dự đoán TSV hoặc vị trí đặt miếng đệm liên kết, đảm bảo các phân vùng thẳng hàng với lưới điện và cây đồng hồ.

- Tác động đến định tuyến : IC 3D làm giảm tình trạng tắc nghẽn định tuyến 2D nhưng lại gây ra những thách thức về kết nối theo chiều dọc, trong khi liên kết lai giảm thiểu cả hai, cho phép giao diện phân vùng dày đặc hơn.

- Khả năng sản xuất : Phân vùng phải tính đến các quy tắc cụ thể của quy trình — ví dụ: vùng cấm TSV trong IC 3D hoặc bước đệm liên kết trong thiết kế lai — điều khiển kích thước và hình dạng khối vật lý.

Ví dụ trong bối cảnh vật lý :

- Được điều khiển bởi AI : Trong SoC máy chủ, AI có thể phân vùng một khối kết nối dày đặc thành hai vùng hình chữ nhật, đặt chúng gần các cạnh đối diện để cân bằng các lớp định tuyến.

- IC 3D : Thiết kế vật lý của SoC di động có thể xếp chồng phân vùng GPU lên trên phân vùng CPU, với các TSV được nhóm ở cạnh dưới của GPU để cung cấp điện.

- Liên kết lai : Bộ tăng tốc AI có thể chia tách vật lý một phân vùng bộ nhớ thành hai khuôn, sử dụng liên kết lai để căn chỉnh các dòng bộ nhớ đệm trực tiếp trên các đơn vị tính toán, cắt giảm độ trễ truy cập.

Kết luận

Phân vùng SoC hiệu quả là nền tảng cho kết quả thiết kế thành công. Bằng cách hiểu rõ các sắc thái của phân vùng logic và phân vùng vật lý, sự khác biệt của chúng và tầm quan trọng của các quyết định đóng băng, các kỹ sư có thể tự tin xử lý sự phức tạp của quá trình phát triển SoC hiện đại.