Sơ đồ cấp xung nhịp

Bài viết này khám phá sơ đồ đồng hồ, đây là chiến lược quản lý tín hiệu thời gian (đồng hồ) giúp đồng bộ hóa các hoạt động của hệ thống kỹ thuật số.

1. Giới thiệu

Nhiều sơ đồ để điều khiển mạch số đồng bộ đã được đưa ra trong nhiều năm. Về lý thuyết, tất cả các flip-flop và bộ nhớ trong miền xung nhịp đều cập nhật trạng thái của chúng đồng thời, nhưng trên thực tế, các cạnh xung nhịp có thể bị phân tán theo thời gian do các hiện tượng như độ lệch xung nhịp và độ dao động xung nhịp. Các sơ đồ này khác nhau về mức độ dễ bị ảnh hưởng bởi các hiệu ứng này, yêu cầu về tài nguyên phần cứng và tác động đến hiệu suất. Truyền dữ liệu đáng tin cậy giữa các mạch con yêu cầu cửa sổ gọi dữ liệu của mạch con nhận phải được bao hàm hoàn toàn bởi cửa sổ dữ liệu hợp lệ của bộ phát. Các sơ đồ xung nhịp rất quan trọng để duy trì thời gian và sự phối hợp chính xác trong các mạch số, vì việc tuân thủ nghiêm ngặt một nguyên tắc xung nhịp nhất quán là tối quan trọng để thiết kế thành công các hệ thống lớn và đáng tin cậy . Việc lựa chọn nguyên tắc xung nhịp và mạng phân phối xung nhịp phải đảm bảo rằng biên độ thiết lập và giữ có thể hấp thụ các hiệu ứng kết hợp của độ lệch và độ dao động trong mọi điều kiện hoạt động , do đó bảo vệ hiệu suất tổng thể của hệ thống.

2. Nguyên tắc cơ bản của việc chấm công trong hệ thống kỹ thuật số

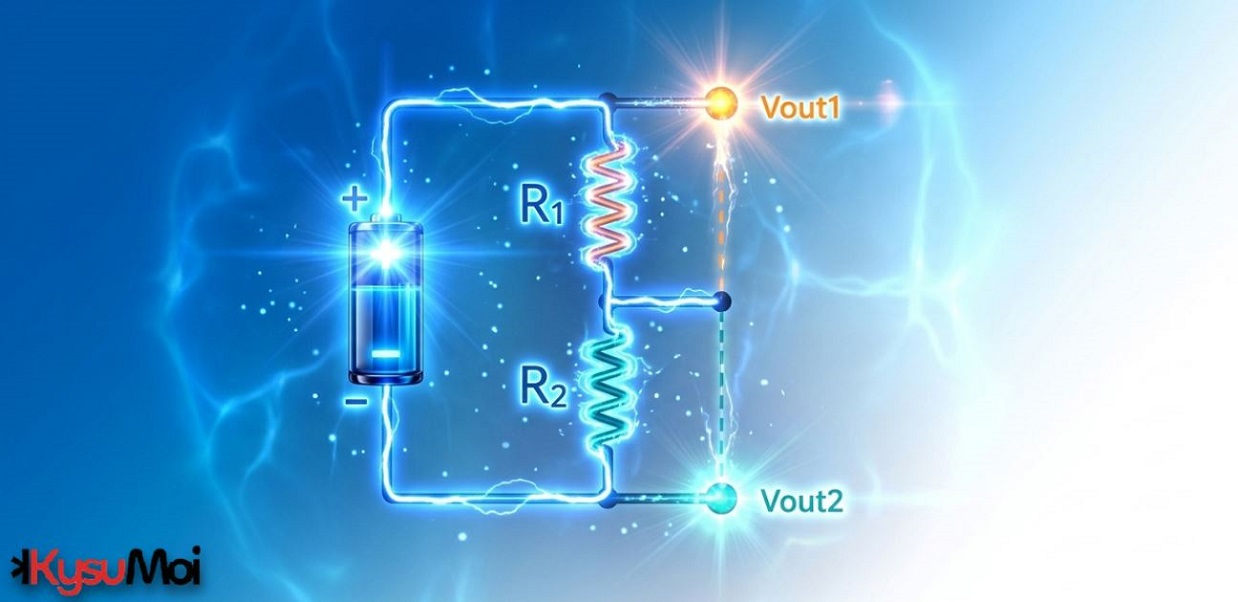

Tín hiệu xung nhịp trong các hệ thống kỹ thuật số thường là sóng vuông tuần hoàn phối hợp hoạt động của các phần tử tuần tự như flip-flop và chốt, đảm bảo quá trình xử lý dữ liệu diễn ra theo thứ tự trong các hệ thống đồng bộ. Đối với xung nhịp kích hoạt bằng hai cạnh, cần có dạng sóng xung nhịp đối xứng nghiêm ngặt, với thời gian thấp và cao mỗi thời gian bằng một nửa chu kỳ xung nhịp, tạo ra chu kỳ hoạt động chính xác bằng một nửa trong mọi điều kiện hoạt động.

Các cạnh xung nhịp, đặc biệt là các chuyển tiếp lên và xuống, rất quan trọng trong việc điều khiển các phần tử logic tuần tự . Các flip-flop kích hoạt theo cạnh, chẳng hạn như flip-flop loại D, chỉ thay đổi trạng thái khi có cạnh xung nhịp, thường là ở cạnh lên, và giữ nguyên đầu ra cho đến cạnh hoạt động tiếp theo. Ngược lại, các chốt có thể nhạy cảm với mức, theo dõi đầu vào khi xung nhịp ở một mức logic cụ thể và giữ nguyên giá trị trong trường hợp ngược lại.

Đồng hồ đồng bộ sử dụng một tín hiệu đồng hồ duy nhất để điều khiển tất cả các chốt nhạy cảm với cạnh và đồng hồ không được kết nối với bất kỳ tín hiệu nào khác. Cách tiếp cận này được ưa chuộng vì trong các mạch đồng bộ được thiết kế hợp lý , các mối nguy hiểm không ảnh hưởng đến chức năng và không xảy ra vi phạm thời gian. Mặt khác, đồng hồ không đồng bộ phức tạp hơn và nhạy cảm hơn với các biến thể trễ , khiến việc dự đoán hành vi của mạch trở nên khó khăn và làm tăng nguy cơ xảy ra các vấn đề về thời gian.

Thời gian thiết lập là khoảng thời gian trước cạnh xung nhịp mà trong đó đầu vào phải duy trì ổn định, trong khi thời gian giữ là khoảng thời gian sau cạnh xung nhịp mà trong đó đầu vào phải tiếp tục hợp lệ.

Điều thực sự quan trọng là nguyên tắc định thời gian và mạng lưới phân phối đồng hồ được lựa chọn sao cho biên độ thiết lập và giữ mà chúng cung cấp có thể hấp thụ các tác động kết hợp của độ lệch và độ nhiễu ở mọi nơi trong miền đồng hồ và trong mọi điều kiện hoạt động .

3. Các loại chương trình chấm công và đặc điểm của chúng

3.1 Đồng hồ một pha kích hoạt cạnh đơn

Xung nhịp một pha kích hoạt một cạnh là phương pháp tự nhiên nhất dựa trên nền tảng lý thuyết automata hoặc thiết kế hệ thống trừu tượng. Các thanh ghi được triển khai từ các flip-flop kích hoạt một cạnh và tất cả đều được kích hoạt bởi cùng một cạnh xung nhịp, được gọi là cạnh chủ động. Mỗi chu kỳ tính toán bắt đầu sau một cạnh xung nhịp chủ động và kết thúc bằng cạnh tiếp theo, do đó chu kỳ tính toán bằng chu kỳ xung nhịp. Sơ đồ này đơn giản về mặt khái niệm nhưng có phạm vi nhỏ đối với độ lệch và độ dao động xung nhịp, đòi hỏi phải cân bằng cẩn thận mạng lưới phân phối xung nhịp và xác minh thời gian. Việc cố định thời gian giữ có thể hữu ích, nhưng các chuỗi bộ đệm mở rộng có thể làm tăng kích thước mạch và lãng phí năng lượng mà không đóng góp vào quá trình tính toán. Bất kỳ sự thay đổi nào so với phương pháp chỉ sử dụng flip-flop kích hoạt một cạnh đơn giản đều làm phức tạp quá trình thiết kế và đòi hỏi nỗ lực kỹ thuật đáng kể hơn .

3.2 Đồng hồ hai pha nhạy cảm với mức

Xung nhịp hai pha nhạy mức, cả đối xứng và không đối xứng, sử dụng các chốt được điều khiển bởi hai tín hiệu xung nhịp không chồng lấn. Các sơ đồ đối xứng chia nhỏ chu kỳ xung nhịp thành bốn khoảng, với dữ liệu chỉ chạy giữa hai tập hợp chốt, tạo thành một đồ thị hai phần . Các khoảng không chồng lấn cung cấp khả năng bảo vệ chống lại độ lệch và độ rung quá mức, và biên độ lệch tự do có thể được thiết kế bằng cách điều chỉnh dạng sóng xung nhịp. Tuy nhiên, điều này đi kèm với chi phí định tuyến, công sức thiết kế bổ sung để phân phối hai tín hiệu xung nhịp và diện tích khuôn tăng lên. Các sơ đồ không đối xứng chuyển logic tổ hợp sang một bên, khiến một số khoảng không hiệu quả nhưng cho phép biên độ lệch lớn, gây ảnh hưởng đến tốc độ hoạt động .

3.3 Máy phát xung nhịp cục bộ Domino và N-Pha chịu được độ lệch

Mạch domino chịu lệch loại bỏ chốt và loại bỏ chi phí phát sinh do lệch xung nhịp, độ trễ chốt và logic mất cân bằng. Các xung nhịp chồng lấn đảm bảo các cổng sẵn sàng hoạt động khi dữ liệu đến, ngay cả khi độ lệch xung nhịp ở mức vừa phải, và cho phép mượn thời gian nếu độ chồng lấn giữa các pha lớn hơn độ lệch xung nhịp. Bộ tạo xung nhịp cục bộ N pha cung cấp một pha cho mỗi cổng, mang lại khả năng chịu lệch tối đa và thời gian nạp trước dài hơn, nhưng phải đánh đổi bằng việc tạo ra và phân phối nhiều xung nhịp hơn, đồng thời cân bằng độ trễ giữa cổng và xung nhịp.

3.4 Đồng hồ trung thời gian

Đồng hồ mesochronous phân phối tín hiệu đồng hồ toàn cục mà không quan tâm nhiều đến độ lệch, sử dụng các mạch đồng bộ hóa cục bộ để lấy mẫu dữ liệu tại nhiều điểm và lưu giữ dữ liệu hợp lệ. Các đường trễ có thể điều chỉnh trong mạng phân phối đồng hồ có thể được hiệu chuẩn khi khởi động để đồng bộ hóa tất cả các khối .

3.5 Hệ thống đồng bộ cục bộ, không đồng bộ toàn cục (GALS)

Hệ thống GALS kết hợp các đảo đồng bộ giao tiếp thông qua các giao thức trao đổi dữ liệu tự định thời gian, sử dụng bộ phân xử và đồng hồ có thể tạm dừng. Kiến trúc GALS đang được nghiên cứu để cải thiện hiệu suất năng lượng , hiệu suất tốt hơn, phân phối đồng hồ dễ quản lý hơn và tái sử dụng thiết kế dễ dàng hơn.

3.6 Cổng đồng hồ để quản lý nguồn điện

Clock gating được sử dụng rộng rãi để quản lý năng lượng. Clock gating dừng xung nhịp của các linh kiện nhàn rỗi, giúp tiết kiệm năng lượng trong các thanh ghi và cổng logic tổ hợp . Về mặt khái niệm, nó đơn giản, có chi phí vận hành thấp và thường không có chi phí vận hành, vì các linh kiện có thể chuyển từ trạng thái nhàn rỗi sang trạng thái hoạt động trong một hoặc vài chu kỳ. Thách thức thiết kế chính là xây dựng các mạch phát hiện trạng thái nhàn rỗi nhỏ, chính xác và thiết kế mạch phân phối xung nhịp có cổng, giảm thiểu chi phí định tuyến và kiểm soát chặt chẽ độ lệch xung nhịp .

4. Phân phối xung nhịp, quản lý độ lệch và cân nhắc về công suất

Việc phân phối tín hiệu xung nhịp trên các mạch tích hợp lớn và bộ xử lý đa lõi đặt ra những thách thức đáng kể do yêu cầu độ lệch và độ dao động xung nhịp thấp, độ dốc xung nhịp nhanh, độ trễ phân phối vừa phải và dung sai đối với các biến thể quy trình, nhiệt độ và điện áp (PTV) cũng như các sắp xếp mạch đa dạng do việc đặt và định tuyến tự động. Tổng hợp cây xung nhịp là điều cần thiết để phân phối xung nhịp đáng tin cậy và nên sử dụng các bộ tạo cây xung nhịp đáng tin cậy để tổng hợp, đặt và định tuyến các mạng xung nhịp, vì các công cụ tổng hợp logic tiêu chuẩn không được thiết kế để xử lý việc phân phối xung nhịp. Xác minh thời gian tĩnh, bao gồm kiểm tra điều kiện thiết lập và giữ, phải được thực hiện bằng cách sử dụng danh sách mạng sau bố trí để tính đến các ký sinh trùng bố trí.

Các kỹ thuật tạo xung nhịp cục bộ , chẳng hạn như bộ tạo xung nhịp đường trễ, được sử dụng để tạo ra các xung nhịp chồng lấn cho domino chịu được độ lệch bằng cách làm trễ các cạnh của xung nhịp toàn cục bằng các chuỗi biến tần. Thiết kế hai pha và bốn pha sử dụng bộ tạo bù lệch thấp và bộ cắt xung nhịp để kéo dài các cạnh xung nhịp, với quạt ra 3–4 trên mỗi phần tử trễ của biến tần để cân bằng độ trễ và diện tích trong khi vẫn duy trì các cạnh sắc nét trong thiết kế hai pha. Bộ tạo xung nhịp phản hồi, chẳng hạn như vòng khóa trễ (DLL), làm giảm thêm độ lệch và độ bất định của chu kỳ nhiệm vụ bằng cách bù cho các biến đổi của quy trình và môi trường , mặc dù DLL tạo ra độ lệch bổ sung và nhạy cảm hơn với nhiễu điện áp so với hệ thống đường trễ.

Vi phạm thời gian thiết lập do đường dẫn dài hoặc độ lệch quá mức được giải quyết bằng cách tăng chu kỳ xung nhịp. Vi phạm thời gian giữ do đường dẫn ngắn hoặc độ lệch quá mức được giải quyết bằng cách tăng độ không chồng chéo giữa các pha. Độ lệch và độ dao động được xác định bởi dạng sóng tín hiệu xung nhịp, và các hệ thống hai pha nhạy cảm với mức có thể hấp thụ các biến thiên thời gian chưa biết bằng cách định cỡ các khoảng không chồng chéo, mặc dù điều này làm tăng chi phí định tuyến và diện tích khuôn.

Clock gating được sử dụng rộng rãi để giảm mức tiêu thụ điện năng , với clock gating phân cấp và điều khiển clock toàn cục được triển khai trong các bộ xử lý như Alpha 21 264 và PowerPC 603. Các bộ xử lý này có thể đóng băng clock thành các thành phần nhàn rỗi, và điều khiển clock toàn cục cho phép vô hiệu hóa clock cho tất cả các đơn vị ở trạng thái ngủ, với thời gian đánh thức phụ thuộc vào việc vòng khóa pha (PLL) đang hoạt động hay tắt. Clock gating tạo ra chi phí hiệu suất tối thiểu, vì clock có thể được khởi động lại bằng cách hủy tín hiệu đóng băng clock và phù hợp với các thành phần tự quản lý với logic phát hiện trạng thái nhàn rỗi tùy chỉnh. Những thách thức thiết kế chính bao gồm xây dựng các mạch phát hiện trạng thái nhàn rỗi nhỏ, chính xác và thiết kế mạch phân phối clock có cổng giúp giảm thiểu chi phí định tuyến và kiểm soát chặt chẽ độ lệch clock.

Trong bộ xử lý đa lõi, việc điều chỉnh điện áp và tần số động (DVFS) có thể được thực hiện trên từng lõi, giúp tăng cường khả năng tiết kiệm điện năng. Vận hành từng lõi độc lập và tắt chúng một cách có chọn lọc cho phép cân bằng giữa công suất động và công suất tĩnh tùy thuộc vào công nghệ quy trình và yêu cầu tính toán.

5. Các chủ đề nâng cao, xu hướng mới nổi và kết luận

Thiết kế mạch không đồng bộ , hoạt động mà không cần cơ chế định thời bên ngoài, cho phép đầu ra phản ứng ngay lập tức với các thay đổi đầu vào và đôi khi được yêu cầu trong các hệ thống mà đầu vào không thể đồng bộ hóa với phần còn lại của mạch hoặc khi độ trễ tín hiệu trong các mạch lớn khiến việc đồng bộ hóa chính xác là không thể. Các mạch này còn được gọi là mạch không xung nhịp hoặc mạch chạy tự do, và tốc độ của chúng chỉ bị giới hạn bởi các đặc tính của các thành phần, mang lại tiềm năng cho tốc độ hoạt động cao hơn so với mạch đồng bộ. Tuy nhiên, mạch không đồng bộ khó thiết kế hơn mạch đồng bộ.

Các phương pháp tạo xung nhịp lai, chẳng hạn như kiến trúc Đồng bộ cục bộ không đồng bộ toàn cục (GALS), kết hợp các đảo đồng bộ giao tiếp không đồng bộ bằng cách sử dụng các giao thức trao đổi dữ liệu tự định thời gian, bộ phân xử và các xung nhịp có thể tạm dừng. Các thiết kế GALS đã được chứng minh là cho phép điều chỉnh điện áp theo mức độ chi tiết, với các nghiên cứu chỉ ra rằng bộ xử lý GALS có năm miền xung nhịp có thể bị giảm hiệu suất từ 5% đến 15%, trong khi đạt được mức giảm tiêu thụ điện năng trung bình là 10%. Trong các kiến trúc này, các đơn vị chức năng khác nhau, chẳng hạn như đơn vị tìm nạp lệnh và đơn vị dấu chấm động , có thể hoạt động ở các tốc độ xung nhịp khác nhau tùy theo nhu cầu về thông lượng và độ trễ của chúng. Có thể kiểm soát phi tập trung các miền khác nhau và việc sử dụng các hàng đợi đầu vào là một chỉ báo tốt cho tần suất hoạt động phù hợp.

Hầu hết các khái niệm và luồng thiết kế đồng hồ lai và không đồng bộ vẫn được coi là nghiên cứu và ngành công nghiệp không muốn áp dụng các khái niệm và luồng thiết kế chưa được chứng minh.