Thiết kế cấp độ chuyển đổi thanh ghi (RTL) là gì?

Thiết kế Cấp độ chuyển đổi thanh ghi (RTL) là một phương pháp mô tả cách dữ liệu di chuyển và xử lý giữa các thanh ghi trong mạch kỹ thuật số.

Thiết kế cấp độ chuyển đổi thanh ghi (RTL) là một bước thiết yếu trong quy trình thiết kế mạch số. Nó xác định và tối ưu hóa chức năng logic của thiết kế số ở cấp độ trừu tượng trước khi xác định bố cục vật lý của mạch. Các kỹ sư chuyển đổi hành vi mong muốn ở cấp độ cao của thiết kế thành mã phần mềm bằng ngôn ngữ mô tả phần cứng (HDL) như VHDL hoặc Verilog .

Các HDL đầu tiên có khả năng mô hình hóa ở cấp độ RTL được phát triển vào những năm 1980 và phát triển thành các hệ thống thiết kế đầy đủ cho phép các kỹ sư mô hình hóa luồng dữ liệu trong các mạch điện tử.

Khi các thiết kế ngày càng lớn hơn và phức tạp hơn, cùng với công nghệ sản xuất cho phép thực hiện các phép toán logic và toán học theo những cách mới, các phương pháp thiết kế RTL cũng bắt kịp xu hướng. Theo thời gian, thiết kế RTL trở thành một bước bắt buộc trong quy trình thiết kế kỹ thuật số, kết nối các bước thiết kế hệ thống và thiết kế mạch.

Bản chất trừu tượng của mô tả RTL cho phép thực hiện các nghiên cứu nhanh chóng và lặp lại thiết kế nhanh chóng để có được thiết kế tối ưu và chấp nhận được trước khi đi sâu vào các giai đoạn phức tạp và tốn thời gian hơn của quy trình thiết kế.

Thiết kế RTL là một phần quan trọng của chu trình thiết kế mạch tích hợp, cho phép các kỹ sư tối ưu hóa thiết kế của họ ở các giai đoạn thanh ghi, toán tử và luồng dữ liệu trước khi họ cần phải quan tâm đến các thành phần vật lý và cách chúng được kết nối. Trong bài viết này, chúng tôi sẽ đề cập đến một số nguyên tắc cơ bản, mô tả vị trí của thiết kế RTL trong thiết kế mạch số và giải thích quy trình thiết kế RTL. Sau đó, chúng tôi sẽ trình bày cách thiết kế RTL phù hợp với thiết kế chip mảng cổng lập trình trường (FPGA) và mạch tích hợp ứng dụng cụ thể (ASIC), đồng thời hé lộ tương lai của thiết kế RTL.

Những nguyên tắc cơ bản của thiết kế RTL

Cụm từ "register-transfer" (chuyển thanh ghi) đề cập đến cách ngôn ngữ mô tả luồng dữ liệu giữa các thanh ghi và cách áp dụng các phép toán logic và toán học vào dữ liệu. Các kỹ sư sử dụng thiết kế RTL để mô tả các khối chức năng, nhằm xác định hành vi của một thành phần rời rạc được sử dụng để thực hiện một chức năng cụ thể. Mỗi khối chức năng có một mô tả về các thanh ghi trong khối, được gọi là mạch tuần tự, và một mạch tổ hợp chứa phép toán logic cho khối chức năng đó. Họ cũng sử dụng HDL để mô tả cách các khối chức năng được kết nối để xác định luồng dữ liệu qua mạch.

Sức mạnh của thiết kế RTL nằm ở cách nó phân chia một hệ thống phức tạp thành các khối tương đối đơn giản được biểu diễn bằng mã HDL. Dưới đây là một số nguyên tắc cơ bản quan trọng để hiểu cách sử dụng thiết kế RTL.

Đăng ký

Trong thiết kế RTL, một thành phần phần cứng có thể lưu trữ một lượng dữ liệu nhất định được gọi là thanh ghi. Chúng thường được triển khai dưới dạng D flip-flop . Giá trị của thanh ghi có thể được đọc làm đầu vào cho một phép toán logic, hoặc có thể được đặt làm đầu ra của một phép toán. Mục đích cơ bản của thiết kế RTL là mô tả cách dữ liệu chảy giữa các thanh ghi và cách dữ liệu bị thay đổi bởi một phép toán.

Ngôn ngữ mô tả phần cứng (HDL)

Phần quan trọng nhất của thiết kế RTL là mã mô tả hành vi của mạch. HDL là một ngôn ngữ đặc tả trông rất giống ngôn ngữ lập trình, với các biến, lệnh gọi hàm, các câu lệnh logic như if-then-else và CASE, các câu lệnh Boolean và toán học. Tuy nhiên, HDL được thiết kế đặc biệt để mô tả hành vi và cấu trúc của mạch điện tử, thường là mạch tích hợp . Một điểm khác biệt giữa HDL và các ngôn ngữ lập trình là khái niệm thời gian được tích hợp trong ngôn ngữ để các hoạt động có thể được kích hoạt bởi đồng hồ trong mạch.

Điều này được thực hiện thông qua việc sử dụng biến xác định giá trị của đồng hồ kỹ thuật số trong mạch, như trong ví dụ đơn giản về bộ biến tần VHDL này, trong đó đầu ra (Q) được đặt thành giá trị đầu vào (D) khi giá trị đồng hồ, clk, chuyển từ trạng thái thấp sang trạng thái cao (cạnh tăng):

D <= not Q;

process(clk)

begin

if rising_edge(clk) then

Q <= D;

end if;

end process;HDL, Ngôn ngữ Mô tả Phần cứng Mạch Tích hợp Tốc độ Rất Cao (VHDL), được sử dụng phổ biến nhất, là một ngôn ngữ dài dòng, có kiểu dữ liệu mạnh với cú pháp không giống ngôn ngữ C. Đây là HDL được ưa chuộng để mô tả các thiết kế hệ thống phức tạp hơn.

Một HDL phổ biến khác là Verilog hoặc siêu tập của nó, SystemVerilog. Verilog ngắn gọn hơn, ít kiểu dữ liệu hơn, linh hoạt hơn và cú pháp của nó trông giống như mã C. Vì dễ học và dễ viết mô tả, các kỹ sư thường sử dụng Verilog khi mới bắt đầu hoặc khi mạch của họ không quá phức tạp. IEEE định nghĩa cả Verilog và VHDL là các tiêu chuẩn công nghiệp.

Sau đây là một ví dụ đơn giản về cổng AND trong cả hai ngôn ngữ. Cổng AND có hai đầu vào và một đầu ra. Nếu cả hai đầu vào đều bằng 1, đầu ra sẽ là 1. Nếu chúng không bằng nhau hoặc nếu cả hai đều được đặt thành 0, đầu ra sẽ là 0.

VHDL mô tả cổng AND như sau:

entity my_and is -- First, you define the entity

port (

inp1: in std_logic; -- The first port

inp2: in std_logic; -- The second port

rst: out std_logic -- The output port

);

end my_and;

architecture blk of my_and is -- Next, define the architecture

begin

process(inp1, inp2) -- With the inputs, do the following

Begin

-- Use a simple if-then-else statement

if((inp1=’1’) and inp1=’1’))then

rst <= ’1’;

else

rst <= ’0’;

End if;

end process

end blk;Verilog cho cổng AND trông như thế này:

module my_and(inp1,inp2,rst); // define the module call

input inp1, inp2; // define inputs and output

output rst;

assign rst = inp1 & inp2; // use the & (and) operator

endmoduleLogic này lấy giá trị ở hai cổng đầu vào và đặt giá trị đầu ra là 1 nếu cả hai cổng đều là 1. Đây là một ví dụ đơn giản, nhưng loại mã này có thể biểu diễn mọi thực thể trong hệ thống và sau đó có thể được kết hợp để định nghĩa toàn bộ mạch số. Các khối xây dựng cơ bản điển hình bao gồm bộ cộng, bộ nhân, bộ đếm, bộ nhớ và máy trạng thái. Sau khi kỹ sư thiết kế định nghĩa hệ thống, mã sẽ được gửi đến trình biên dịch. Nếu biên dịch không có lỗi, kỹ sư có thể sử dụng kết quả để kiểm tra hệ thống.

Các phép toán logic

Có hai loại phép toán trong thiết kế RTL. Loại thứ nhất, phép toán logic, thực hiện đánh giá và sửa đổi từng bit dữ liệu được lưu trữ trong các thanh ghi. Các phép toán logic như AND, OR, NOT, XOR và shift được tạo ra bằng cách định nghĩa hành vi logic trong HDL. Ví dụ trên cho thấy cách AND có thể được biểu diễn trong VHDL và Verilog. Các phép toán logic biểu diễn các cổng logic trong phần cứng.

Các phép tính số học

Loại phép toán thứ hai trong thiết kế RTL là các phép toán số học. Chúng lấy dữ liệu trong các thanh ghi và cộng, trừ, nhân, chia. Chúng được biểu diễn trong HDL bằng các toán tử toán học tiêu chuẩn. Ví dụ, việc cộng hai số trong VHDL sẽ sử dụng dòng lệnh:

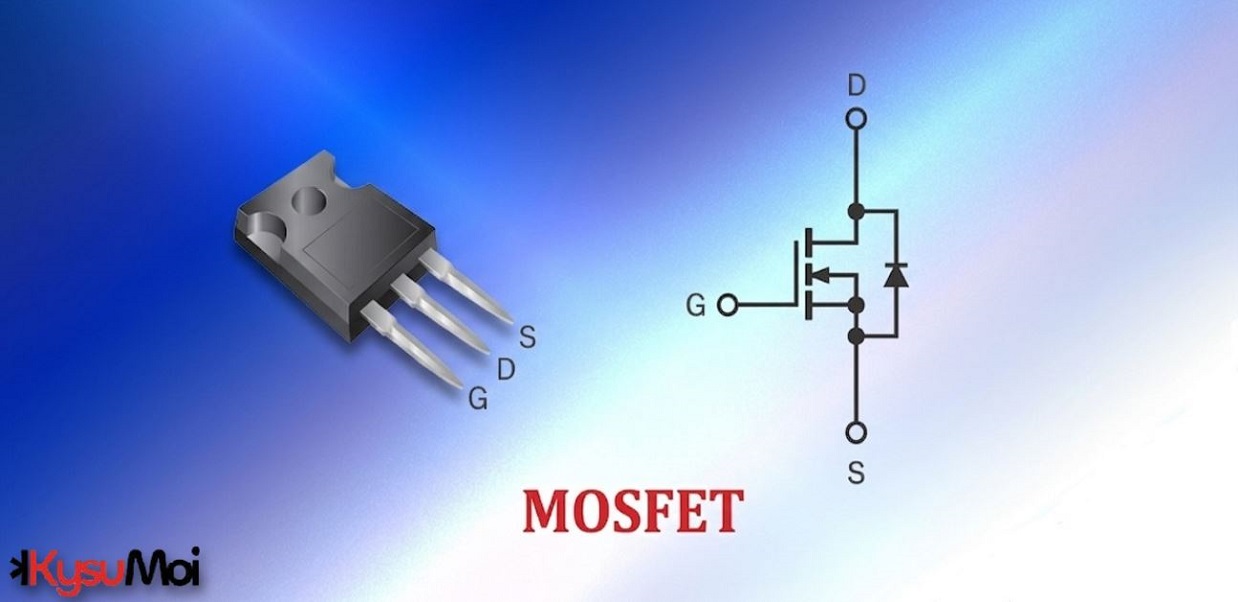

rst <= inp1 + inp2;— trong đó inp1 và inp2 là hai thanh ghi đầu vào, và rst được gán cho thanh ghi đầu ra. Các phép toán số học trong RTL biểu diễn các thành phần vật lý chuyên dụng như bộ cộng, bộ trừ, bộ nhân và bộ chia.

Hành động đồng bộ và không đồng bộ

Thiết kế RTL có thể biểu diễn luồng dữ liệu theo cả hai cách đồng bộ và bất đồng bộ. Đối với đồng bộ, một chương trình con được thực thi hoặc kích hoạt bởi đầu vào xung nhịp hệ thống cho hàm. Đối với bất đồng bộ, chương trình con được thực thi khi giá trị của một hoặc nhiều cổng đầu vào thay đổi theo một cách cụ thể. Điều này được thực hiện bằng cách kiểm tra các giá trị đầu vào của đầu vào xung nhịp hoặc các đầu vào không phải xung nhịp để xem chúng có thay đổi hay không bằng câu lệnh if.

Vai trò của RTL trong thiết kế mạch tích hợp

Quy trình thiết kế mạch tích hợp (IC) hiện đại bao gồm việc lấy thông số kỹ thuật về những gì thiết bị cần làm và biến nó thành một chip bán dẫn đóng gói. Mức độ trừu tượng mà thiết kế RTL mang lại cho phép các kỹ sư tập trung vào các chức năng cấp cao hơn của hệ thống mà không cần phải xem xét các chi tiết cụ thể về cách triển khai thiết kế về mặt vật lý.

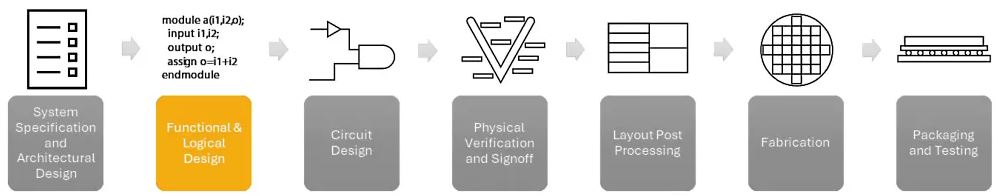

Bước đầu tiên trong quy trình thiết kế IC là xác định thông số kỹ thuật hệ thống và thiết kế kiến trúc. Thông tin này được chuyển đổi thành mã HDL. Sau đó, các kỹ sư sử dụng mã đó để xác định thiết kế chức năng và logic. Sau khi hoàn tất, thiết kế được chuyển đổi thành netlist, sau đó được sử dụng để tạo thiết kế mạch, tiếp theo là phần còn lại của quy trình thiết kế.

Việc biểu diễn trừu tượng bằng thiết kế RTL được thực hiện càng sớm càng tốt trong quá trình thiết kế — trước khi đầu tư thời gian và tiền bạc vào thiết kế vật lý, xác minh thiết kế vật lý hoặc chế tạo phần cứng thực tế. Việc tích hợp bước thiết kế RTL vào quy trình đòi hỏi sự tích hợp tốt giữa đặc tả hệ thống lúc đầu và các công cụ mạnh mẽ giúp chuyển đổi các thanh ghi, thao tác và luồng dữ liệu thành mạch thực tế khi thiết kế RTL hoàn tất.

Luồng thiết kế RTL

Mục tiêu của luồng thiết kế RTL là xác định và tối ưu hóa chức năng của một mạch tích hợp, thường là thiết bị FPGA hoặc ASIC. Các kỹ sư thiết kế sử dụng luồng thiết kế RTL để trước tiên xác định logic và luồng của thiết bị nhằm kiểm tra và tối ưu hóa hệ thống, sau đó chuyển đổi định nghĩa RTL thành netlist. Năm bước sau đây xác định phương pháp thiết kế RTL điển hình.

1. Tổng hợp cấp cao

Nhiệm vụ đầu tiên trong quy trình là chuyển đổi các thông số kỹ thuật cho thiết bị thành mã HDL với càng ít chỉnh sửa càng tốt. Trong hầu hết các trường hợp, các kỹ sư biểu diễn hành vi mong muốn của thiết bị bằng một ngôn ngữ lập trình chuẩn như C hoặc C++. Sau đó, một công cụ phần mềm sẽ phân tích các thuật toán trong mô hình phần mềm thành ngôn ngữ thông số kỹ thuật đã chọn. Bước này có thể bỏ qua đối với các thiết kế đơn giản, nhưng đối với các thiết kế phức tạp hơn, nó có thể tiết kiệm đáng kể công sức.

2. Mã hóa RTL

Sau đó, các kỹ sư tạo hoặc tinh chỉnh mã. Các nhà thiết kế đi sâu vào chi tiết của các thanh ghi cụ thể, các thao tác cần thiết và cách dữ liệu chảy. Một phần quan trọng của bước này là sử dụng các mô-đun để mô tả các thao tác chung và các phần cụ thể của hệ thống. Sau khi tạo xong mô-đun, nó có thể được tái sử dụng khi cần thiết, giúp đơn giản hóa đáng kể độ phức tạp của thiết kế tổng thể.

3. Tối ưu hóa hiệu suất, công suất và diện tích (PPA)

Sau khi hoàn tất mã hóa, quá trình tối ưu hóa sẽ bắt đầu. Mục tiêu của bước này là cải thiện hiệu suất, giảm thiểu mức tiêu thụ điện năng và giảm kích thước vật lý của thiết kế.

Mô phỏng thời gian và logic

Các công cụ mô phỏng được sử dụng để phân tích thời gian và theo dõi các giá trị thanh ghi trong toàn bộ hệ thống. Thiết kế được kiểm tra ở cấp độ chuyển thanh ghi để đảm bảo không có vấn đề về thời gian trên toàn mạch và các hoạt động tạo ra đầu ra mong đợi. Đây là nơi nhóm thiết kế làm việc để gỡ lỗi bất kỳ sự cố nào, bao gồm cả sự cố nguồn , trong hệ thống càng sớm càng tốt trong quá trình thiết kế.

Ước tính công suất

Mỗi thiết bị trong hệ thống đều tiêu thụ một lượng điện năng nhất định, và các kỹ sư thiết kế cần biết lượng điện năng tiêu thụ và lặp lại thiết kế để hiểu rõ sự phân phối điện năng và giảm thiểu mức tiêu thụ điện năng. Phần mềm Ansys PowerArtist™ được nhiều công ty thiết kế bán dẫn hàng đầu sử dụng để phân tích, lập hồ sơ và giảm công suất ở cấp độ thanh ghi-chuyển giao. Phần mềm này mang lại tốc độ xử lý nhanh chóng, cho phép các nhóm thiết kế phân tích và phân chia công suất, xác định mã RTL không hiệu quả về điện năng và gắn thẻ mọi nút chuyển đổi lãng phí trong thiết kế.

Giảm thiểu diện tích

Mỗi thành phần trong mạch tích hợp đều chiếm không gian vật lý, cũng như cách định tuyến giữa các thành phần đó. Mặc dù quy trình thiết kế RTL không xem xét kích thước vật lý của các thành phần, nhưng nó nắm bắt được số lượng thành phần và độ phức tạp của các kết nối giữa chúng.

4. Xác minh

Sau khi thiết kế được tối ưu hóa, cần phải kiểm tra lại để đảm bảo tất cả các thông số kỹ thuật đều được đáp ứng. Đây là một phần quan trọng của quy trình thiết kế, và tất cả các yêu cầu thiết kế phải được kiểm tra trước khi thiết kế có thể được triển khai. Việc này có thể được thực hiện bằng mô phỏng RTL hoặc kiểm tra chính thức.

Mô phỏng RTL: Nhiều công cụ phần mềm khác nhau được sử dụng để kiểm tra thiết kế một cách động. Các vectơ đầu vào được áp dụng và các vectơ đầu ra thu được được so sánh với kết quả mong đợi. Đầu vào và đầu ra thường được biểu diễn dưới dạng sóng để kỹ sư thiết kế có thể kiểm tra trực quan hoạt động của hệ thống.

Xác minh hình thức: Đây là một quy trình xác minh tĩnh sử dụng tự động hóa để chuyển đổi một tập hợp các kỳ vọng về hành vi thành các thuật toán toán học khám phá toàn bộ không gian vận hành của hệ thống. Sau đó, kết quả được đánh giá bằng toán học để xác minh tính chính xác.

5. Tổng hợp RTL

Sau khi thiết kế hệ thống được xác minh đầy đủ, tổng hợp RTL được sử dụng để chuyển đổi biểu diễn mã HDL của thiết kế RTL thành danh sách mạng cấp cổng. Đây là giao diện cho các công cụ chuyển đổi sơ đồ mạch điện kết quả thành bố cục vật lý trong công cụ tự động hóa thiết kế điện tử (EDA). Các công ty như Synopsys đã tích hợp nhiều công cụ tổng hợp vào nền tảng EDA.

Sử dụng thiết kế RTL trong quy trình thiết kế FPGA và ASIC

Mạch tích hợp có thể được chia thành hai loại. Mạch tích hợp ứng dụng chuyên biệt ( ASIC ) được thiết kế riêng cho các ứng dụng hoặc tác vụ cụ thể. Một khi đã được chế tạo, logic trong chip không thể thay đổi. Ví dụ về chip ASIC là các mô-đun bộ nhớ, máy ghi âm kỹ thuật số, bộ xử lý tín hiệu được tối ưu hóa, bộ vi xử lý, bộ xử lý trung tâm (CPU), hoặc thậm chí là một hệ thống phức tạp như hệ thống trên chip bao gồm I/O, CPU, bộ nhớ, v.v.

Chip FPGA (Field-programmable Gate Array) là chip bán dẫn có thể lập trình lại sau khi sản xuất. Thay vì logic được tích hợp sẵn vào hình dạng bên trong chip, FPGA có các mảng khối logic được kết nối bằng một lưới kết nối cũng có thể lập trình được.

Thiết kế RTL đóng vai trò giống nhau trong phần đầu của cả hai luồng thiết kế. Sau khi quá trình tổng hợp RTL hoàn tất, luồng thiết kế ASIC yêu cầu các kỹ sư lập kế hoạch và bố trí các mạch vật lý, được gọi là quy hoạch mặt bằng. Trong thiết kế FPGA, mã RTL được chuyển đổi trực tiếp thành một netlist (danh sách mạng) nhận biết các khối logic nào khả dụng và cấu hình các khối đó trong bước đặt và định tuyến.

Tương lai của thiết kế RTL

Việc sử dụng ngôn ngữ mô tả phần cứng để biểu diễn hành vi mong muốn của các hệ thống số bắt đầu từ những năm 1970 và 1980. Ngôn ngữ này được ưa chuộng đáng kể khi tích hợp quy mô rất lớn (VLSI) ngày càng phổ biến và bắt kịp với những phát triển trong thiết kế IC. Khi kích thước linh kiện trong mạch tích hợp tiếp tục thu hẹp, tốc độ xung nhịp tiếp tục tăng và nhiều chức năng hơn được tích hợp vào một chip, các kỹ sư thiết kế phải đối mặt với những thách thức ngày càng tăng.

Độ phức tạp trong thiết kế vẫn chưa hề giảm sút, và các công cụ RTL vẫn đang tiếp tục phát triển để đáp ứng những thách thức này. Các công ty phát triển bộ công cụ mà các nhà thiết kế sẽ sử dụng để định hình thế hệ mạch tích hợp tiếp theo sẽ tập trung vào một số lĩnh vực chính để cải thiện tính dễ sử dụng, khả năng và chức năng của quy trình thiết kế RTL. Một số lĩnh vực trọng tâm bao gồm:

• Giảm công suất

- Quản lý năng lượng tiếp tục là một trong những thách thức lớn nhất trong toàn bộ quy trình thiết kế mạch tích hợp, và tối ưu hóa RTL tiếp tục là giải pháp tối ưu để hiểu và quản lý các mức sụt áp tiêu thụ điện năng trong hệ thống. Các cải tiến cho các công cụ như phần mềm PowerArtist , mang đến nhiều tùy chọn hơn, khả năng hiển thị tốt hơn và tốc độ nhanh hơn, sẽ giúp các nhóm giải quyết thách thức này.

• Tích hợp liền mạch giữa các công cụ

- Khi số lượng công cụ thiết kế, mô phỏng, xác minh và phê duyệt tăng lên, khả năng của các công cụ hiện có cũng sẽ tăng lên. Các công ty cung cấp các công cụ này và các tổ chức công nghiệp như IEEE sẽ cần phải theo kịp bằng cách cập nhật và cải thiện các tiêu chuẩn, đồng thời cung cấp các công cụ giúp luồng dữ liệu giữa các ứng dụng trở nên liền mạch nhất có thể.

• Bao gồm AI vào Luồng thiết kế

- Nhiều công cụ được sử dụng trong quy trình thiết kế mạch tích hợp đã sử dụng các dạng học máy (ML) và hệ thống chuyên gia để tăng tốc các bước quy trình, đặc biệt là trong việc bố trí mạch vật lý. Điều này sẽ tiếp tục với các thuật toán ML được cải tiến và việc sử dụng các công cụ trí tuệ nhân tạo (AI) để đề xuất các bước tiếp theo hoặc giải pháp khả thi nhất cho các vấn đề.

• Cải tiến cho Tổng hợp cấp cao

- Các nhà cung cấp trong lĩnh vực RTL đang nỗ lực cải thiện khả năng của các kỹ sư trong việc chuyển đổi thông số kỹ thuật hệ thống cấp cao sang ngôn ngữ phần cứng cấp cao với tốc độ nhanh hơn và thiết kế gần với cấu hình tối ưu hơn.

• Tổng hợp RTL thông minh hơn

- Sẽ có khả năng tăng đáng kể năng suất và tối ưu hóa khi các cổng trong mô tả RTL được chuyển đổi thành các bóng bán dẫn thực tế trong bước tổng hợp RTL. Khi hình học vật lý được đưa vào thiết kế, sẽ có cơ hội đưa ra các quyết định sáng suốt giúp đơn giản hóa các quy trình tiếp theo trong việc bố trí mạch.