Thiết kế giao diện kỹ thuật số đáng tin cậy cho ADC xấp xỉ liên tiếp

Bài viết này sẽ giúp các nhà thiết kế tìm hiểu nguyên nhân gốc rễ và đưa ra giải pháp.

Giới thiệu

Bộ chuyển đổi tương tự sang số xấp xỉ liên tiếp, được gọi là ADC SAR do có thanh ghi xấp xỉ liên tiếp, phổ biến cho các ứng dụng yêu cầu độ phân giải lên đến 18 bit với tốc độ lên đến 5 MSPS. Ưu điểm của chúng bao gồm kích thước nhỏ, công suất thấp, không có độ trễ đường ống và dễ sử dụng.

Bộ xử lý chủ có thể truy cập hoặc điều khiển ADC thông qua nhiều giao diện nối tiếp và song song như SPI, I2C và LVDS. Bài viết này thảo luận về các kỹ thuật thiết kế cho giao diện số tích hợp, đáng tin cậy, bao gồm mức và trình tự cấp nguồn số, trạng thái I/O khi bật, thời gian giao diện, chất lượng tín hiệu và lỗi do hoạt động số gây ra.

Cấp độ và trình tự nguồn điện I/O kỹ thuật số

Hầu hết các ADC SAR đều có đầu vào nguồn I/O kỹ thuật số riêng biệt, VIO hoặc VDRIVE, quyết định điện áp hoạt động và khả năng tương thích logic của giao diện. Chân này phải có cùng điện áp với nguồn cung cấp cho giao diện máy chủ (MCU, DSP hoặc FPGA). Các đầu vào kỹ thuật số thường nằm trong khoảng DGND - 0,3 V và VIO+ 0,3 V để tránh vi phạm định mức tối đa tuyệt đối. Các tụ tách ghép có mạch ngắn nên được kết nối giữa chân VIO và DGND.

Các ADC hoạt động với nhiều nguồn cấp có thể có trình tự cấp nguồn được xác định rõ ràng. Ghi chú Ứng dụng AN-932, Trình tự Cấp nguồn , cung cấp tài liệu tham khảo hữu ích cho việc thiết kế nguồn cấp cho các ADC này. Để tránh phân cực thuận cho các diode ESD và cấp nguồn cho lõi kỹ thuật số ở trạng thái không xác định, hãy bật nguồn I/O trước mạch giao diện. Nguồn cấp analog thường được cấp nguồn trước nguồn I/O, nhưng không phải tất cả các ADC đều như vậy. Đọc và làm theo bảng dữ liệu để đảm bảo trình tự chính xác.

Trạng thái I/O kỹ thuật số khi bật

Để khởi tạo đúng cách, một số ADC SAR yêu cầu các trạng thái logic hoặc trình tự nhất định cho các chức năng số như reset, standby hoặc tắt nguồn. Sau khi tất cả nguồn điện ổn định, xung hoặc tổ hợp xung được chỉ định sẽ được áp dụng để đảm bảo ADC khởi động ở trạng thái mong muốn. Ví dụ, cần một xung cao ở chế độ RESET, với thời lượng ít nhất 50 ns, để cấu hình AD7606 hoạt động bình thường sau khi bật nguồn.

Không nên bật/tắt chân digital cho đến khi tất cả nguồn điện được thiết lập đầy đủ. Đối với ADC SAR, chân khởi động chuyển đổi, CNVST, có thể nhạy cảm với nhiễu. Hình 1 cho thấy một ví dụ trong đó cPLD của máy chủ đưa CNVST lên mức cao trong khi AVCC, DVCC và VDRIVE vẫn đang tăng tốc. Điều này có thể khiến AD7367 rơi vào trạng thái không xác định, vì vậy máy chủ nên giữ CNVST ở mức thấp cho đến khi tất cả nguồn điện được thiết lập đầy đủ.

Thời gian giao diện kỹ thuật số

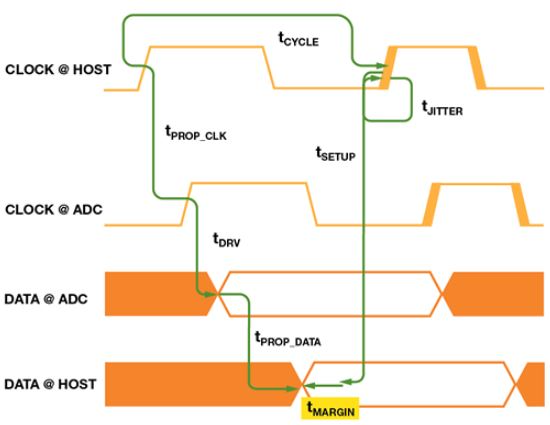

Sau khi quá trình chuyển đổi hoàn tất, máy chủ có thể đọc dữ liệu qua giao diện nối tiếp hoặc song song. Để đọc dữ liệu chính xác, hãy tuân theo một chiến lược thời gian cụ thể, chẳng hạn như chế độ sử dụng cho bus SPI. Không vi phạm các thông số kỹ thuật về thời gian giao diện số, đặc biệt là thời gian thiết lập và thời gian giữ của ADC và máy chủ. Tốc độ bit tối đa được xác định bởi toàn bộ chu kỳ, không chỉ chu kỳ xung nhịp tối thiểu được chỉ định. Hình 2 và các phương trình sau đây minh họa một ví dụ về cách tính toán biên độ thời gian thiết lập và giữ. Máy chủ gửi xung nhịp đến ADC và đọc dữ liệu đầu ra từ ADC.

tCYCLE = tJITTER + tSETUP + tPROP_DATA + tPROP_CLK + tDRV + tMARGIN

tCYCLE: Clock period = 1/fCLOCK

tJITTER: Clock jitter

tSETUP: Thời gian thiết lập máy chủ

tHOLD: Thời gian giữ máy chủ

tPROP_DATA: Độ trễ truyền dữ liệu dọc theo đường truyền từ ADC đến máy chủ

tPROP_CLK: Độ trễ lan truyền xung nhịp dọc theo đường truyền từ máy chủ đến ADC

tDRV: Thời gian hợp lệ đầu ra dữ liệu sau khi xung nhịp tăng/giảm

tMARGIN: Thời gian biên, ≥ 0 nghĩa là thời gian thiết lập hoặc thời gian giữ đã được đáp ứng; < 0 nghĩa là thời gian thiết lập hoặc thời gian giữ không được đáp ứng.

Biên độ thiết lập cho máy chủ là

tMARGIN_SETUP = tCYCLE, phút – tJITTER – tSETUP – tPROP_DATA – tPROP_CLK – tDRV, MAX

Phương trình thời gian thiết lập xác định thời gian chu kỳ xung nhịp tối thiểu hoặc tần số tối đa theo độ trễ hệ thống tối đa. Giá trị này phải ≥ 0 để đáp ứng các thông số kỹ thuật về thời gian. Tăng chu kỳ (giảm tần số xung nhịp) để xử lý độ trễ hệ thống quá mức. Đối với bộ đệm, bộ dịch mức, bộ cách ly hoặc các thành phần bổ sung khác trên bus, hãy thêm độ trễ bổ sung vào tPROP_CLK và tPROP_DATA.

Tương tự như vậy, biên độ giữ cho máy chủ là

tMARGIN_HOLD = tPROP_DATA + tPROP_CLK + tDRV – tJITTER – tHOLD

Phương trình thời gian giữ xác định yêu cầu độ trễ hệ thống tối thiểu để tránh lỗi logic do vi phạm giữ. Độ trễ này phải ≥ 0 để đáp ứng các thông số kỹ thuật về thời gian.

Nhiều ADC SAR của ADI có giao diện SPI sẽ theo dõi MSB từ cạnh giảm của CS hoặc CNV, trong khi các bit dữ liệu còn lại theo cạnh giảm của SCLK, như thể hiện trong Hình 3. Khi đọc dữ liệu MSB, hãy sử dụng ten trong các phương trình thay vì tDRV.

Do đó, ngoài tốc độ xung nhịp tối đa, tốc độ hoạt động tối đa của giao diện kỹ thuật số còn phụ thuộc vào thời gian thiết lập, thời gian giữ, thời gian hợp lệ đầu ra dữ liệu, độ trễ lan truyền và độ dao động xung nhịp.

Hình 4 cho thấy một máy chủ DSP truy cập AD7980 ở chế độ CS 3 dây, với VIO = 3,3 V. DSP chốt tín hiệu SDO trên cạnh xuống của SCLK. DSP chỉ định thời gian thiết lập tối thiểu 5 ns và thời gian giữ tối thiểu 2 ns. Đối với một bo mạch PC FR-4 thông thường, độ trễ lan truyền là khoảng 180 ps/in. Độ trễ lan truyền của bộ đệm là 5 ns. Tổng độ trễ lan truyền cho CNV, SCLK và SDO là

tprop = 180 ps/in × (9 in + 3 in) + 5 ns = 7 ns.

tJITTER = 1 ns. Máy chủ chạy SCLK ở tần số 30 MHz, do đó tCYCLE = 33 ns.

tSETUP_MARGIN = 33 ns − 1 ns – 5 ns – 7 ns – 11 ns – 7 ns = 2 ns

tHOLD_MARGIN =11 ns + 7 ns + 7 ns – 1 ns – 2 ns = 22 ns

Biên độ thiết lập và giữ đều dương, do đó SPI SCLK có thể chạy ở tần số 30 MHz.

Chất lượng tín hiệu số

Tính toàn vẹn tín hiệu số, bao gồm cả thời gian và chất lượng tín hiệu, đảm bảo rằng tín hiệu: được nhận ở mức điện áp quy định; không gây nhiễu lẫn nhau; không làm hỏng các thiết bị khác; và không làm ô nhiễm phổ điện từ. Chất lượng tín hiệu được xác định bằng nhiều thuật ngữ, như minh họa trong Hình 5. Phần này sẽ giới thiệu về hiện tượng quá áp, đổ chuông, phản xạ và nhiễu xuyên âm.

Phản xạ là kết quả của sự không tương thích trở kháng. Khi tín hiệu truyền dọc theo đường truyền, trở kháng tức thời thay đổi tại mỗi giao diện. Một phần tín hiệu sẽ phản xạ trở lại, và một phần sẽ tiếp tục truyền xuống đường truyền. Phản xạ có thể gây ra hiện tượng vượt ngưỡng, thiếu ngưỡng, đổ chuông và các cạnh xung nhịp không đơn điệu tại bộ thu.

Điện áp quá mức và quá thấp có thể làm hỏng mạch bảo vệ đầu vào hoặc làm giảm tuổi thọ của IC. Hình 6 cho thấy định mức tối đa tuyệt đối của AD7606. Điện áp đầu vào kỹ thuật số phải nằm trong khoảng từ –0,3 V đến VDRIVE + 0,3 V. Ngoài ra, việc đổ chuông trên VIL tối đa hoặc dưới VIH tối thiểu có thể gây ra lỗi logic.

Để giảm thiểu sự phản xạ:

- Làm cho dấu vết càng ngắn càng tốt

- Kiểm soát trở kháng đặc trưng của dấu vết

- Loại bỏ phần còn lại

- Sử dụng một chương trình chấm dứt phù hợp

- Sử dụng kim loại đặc có diện tích vòng lặp nhỏ làm mặt phẳng tham chiếu dòng điện trở về

- Sử dụng dòng điện truyền động và tốc độ thay đổi thấp hơn

Có nhiều công cụ phần mềm hoặc trang web để tính toán trở kháng đặc trưng của một đường mạch, chẳng hạn như bộ giải trường đường truyền PCB Si9000 của Polar Instruments. Những công cụ này giúp dễ dàng xác định trở kháng đặc trưng bằng cách chọn mô hình đường truyền và thiết lập các thông số như loại và độ dày điện môi, chiều rộng, độ dày và khoảng cách của đường mạch.

IBIS là một tiêu chuẩn mới nổi được sử dụng để mô tả hành vi tương tự của các ngõ vào/ra số của IC. ADI cung cấp các mô hình IBIS cho các ADC SAR. Mô phỏng trước khi bố trí kiểm tra phân phối xung nhịp, loại gói chip, cách sắp xếp bo mạch, cấu trúc mạng và các chiến lược kết thúc. Nó cũng có thể kiểm tra các ràng buộc về thời gian của giao diện nối tiếp để định hướng vị trí và bố trí. Mô phỏng sau khi bố trí xác minh rằng thiết kế đáp ứng tất cả các hướng dẫn và ràng buộc, đồng thời kiểm tra các vi phạm như phản xạ, rung và nhiễu xuyên âm.

Hình 7 cho thấy một trình điều khiển được kết nối với SCLK1 thông qua đường dây vi mạch 12 inch và trình điều khiển thứ hai được kết nối với SCLK2 thông qua điện trở 43 Ω nối tiếp với vi mạch.

Hình 8 cho thấy một xung quá mức lớn trên SCLK1, vi phạm định mức tối đa tuyệt đối từ -0,3 V đến +3,6 V. Điện trở nối tiếp làm giảm tốc độ thay đổi trên SCLK2, giữ cho tín hiệu nằm trong thông số kỹ thuật.

Nhiễu xuyên âm là sự kết hợp năng lượng giữa các đường truyền song song thông qua điện dung tương hỗ (điện trường) hoặc độ tự cảm tương hỗ (từ trường). Mức độ nhiễu xuyên âm phụ thuộc vào thời gian tăng của tín hiệu, độ dài của các đường truyền song song và khoảng cách giữa chúng.

Một số biện pháp phổ biến để kiểm soát nhiễu xuyên âm là:

- Tăng khoảng cách dòng

- Giảm thiểu chạy song song

- Giữ các dấu vết gần với các mặt phẳng kim loại tham chiếu

- Sử dụng một chương trình chấm dứt phù hợp

- Giảm tốc độ thay đổi của tín hiệu

Sự suy giảm hiệu suất do hoạt động số gây ra

Hoạt động kỹ thuật số có thể làm giảm hiệu suất của ADC SAR, với SNR giảm do nguồn điện hoặc đất kỹ thuật số bị nhiễu, độ nhiễu xung nhịp lấy mẫu và nhiễu tín hiệu kỹ thuật số.

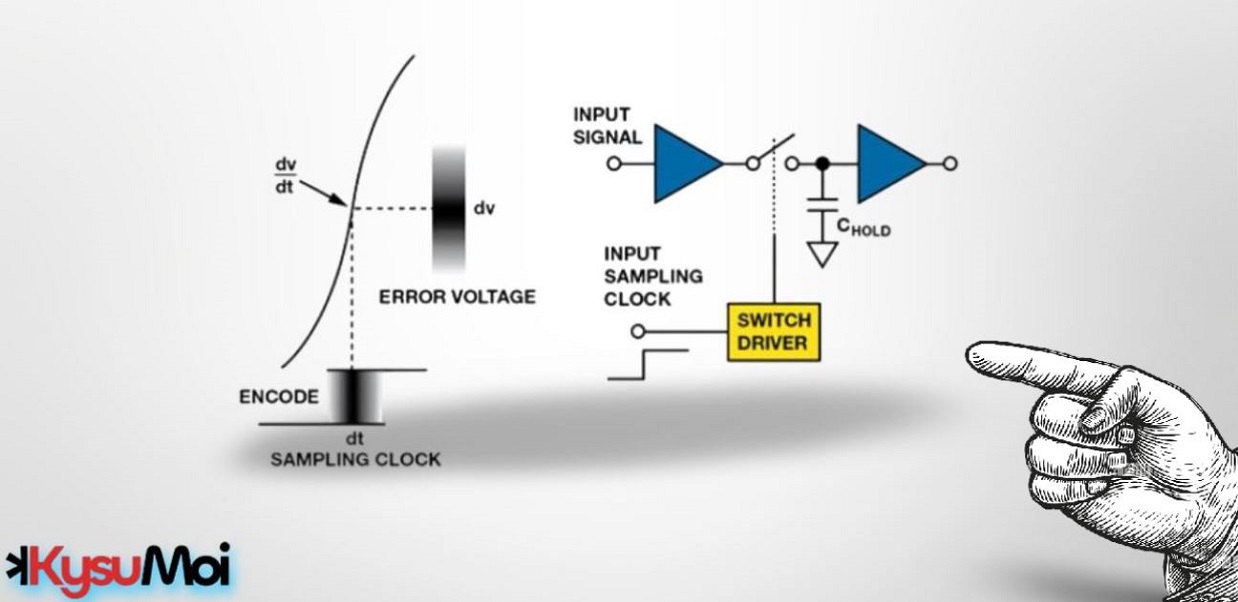

Độ rung khẩu độ hoặc độ rung đồng hồ lấy mẫu đặt giới hạn cho SNR, đặc biệt đối với tín hiệu đầu vào tần số cao. Độ rung hệ thống đến từ hai nguồn: độ rung khẩu độ từ mạch theo dõi và giữ trên chip (độ rung nội bộ) và độ rung trên đồng hồ lấy mẫu (độ rung ngoài). Độ rung khẩu độ là sự thay đổi thời gian lấy mẫu giữa các lần chuyển đổi và là một hàm của bộ ADC. Độ rung đồng hồ lấy mẫu thường là nguồn sai số chính, nhưng cả hai nguồn đều gây ra sự thay đổi thời gian lấy mẫu đầu vào analog, như thể hiện trong Hình 9. Tác động của chúng là không thể phân biệt được.

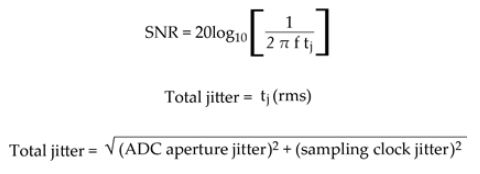

Độ nhiễu tổng thể tạo ra điện áp lỗi, với SNR tổng thể của ADC bị giới hạn bởi

trong đó, f là tần số đầu vào tương tự và tj là độ dao động xung nhịp tổng thể.

Ví dụ, với đầu vào tương tự 10 kHz và độ nhiễu tổng cộng là 1 ns, SNR bị giới hạn ở mức 84 dB.

Tiếng ồn nguồn điện do chuyển mạch đầu ra kỹ thuật số phải được cách ly khỏi nguồn điện analog nhạy cảm. Tách riêng nguồn điện analog và nguồn điện kỹ thuật số, chú ý cẩn thận đến đường dẫn dòng điện trở về đất.

Bộ ADC SAR độ chính xác cao có thể nhạy cảm với hoạt động trên giao diện kỹ thuật số, ngay cả khi nguồn điện được tách rời và cách ly đúng cách. Đồng hồ burst thường hoạt động tốt hơn đồng hồ continuous. Bảng dữ liệu thường hiển thị thời gian im lặng khi giao diện không nên hoạt động. Việc giảm thiểu hoạt động kỹ thuật số trong những khoảng thời gian này - thường là thời điểm lấy mẫu và khi các quyết định bit quan trọng xảy ra - có thể là một thách thức ở tốc độ thông lượng cao hơn.

Phần kết luận

Hãy chú ý cẩn thận đến hoạt động số hóa để đảm bảo chuyển đổi hợp lệ từ ADC SAR. Các lỗi do số hóa có thể khiến ADC SAR rơi vào trạng thái không xác định, gây ra trục trặc hoặc làm giảm hiệu suất. Bài viết này sẽ giúp các nhà thiết kế tìm hiểu nguyên nhân gốc rễ và đưa ra giải pháp.