Thiết kế IC công suất thấp: Kỹ thuật và thực hành tốt nhất

Bài viết này trình bày các kỹ thuật thiết kế thiết yếu và các phương pháp tốt nhất để áp dụng chúng một cách hiệu quả.

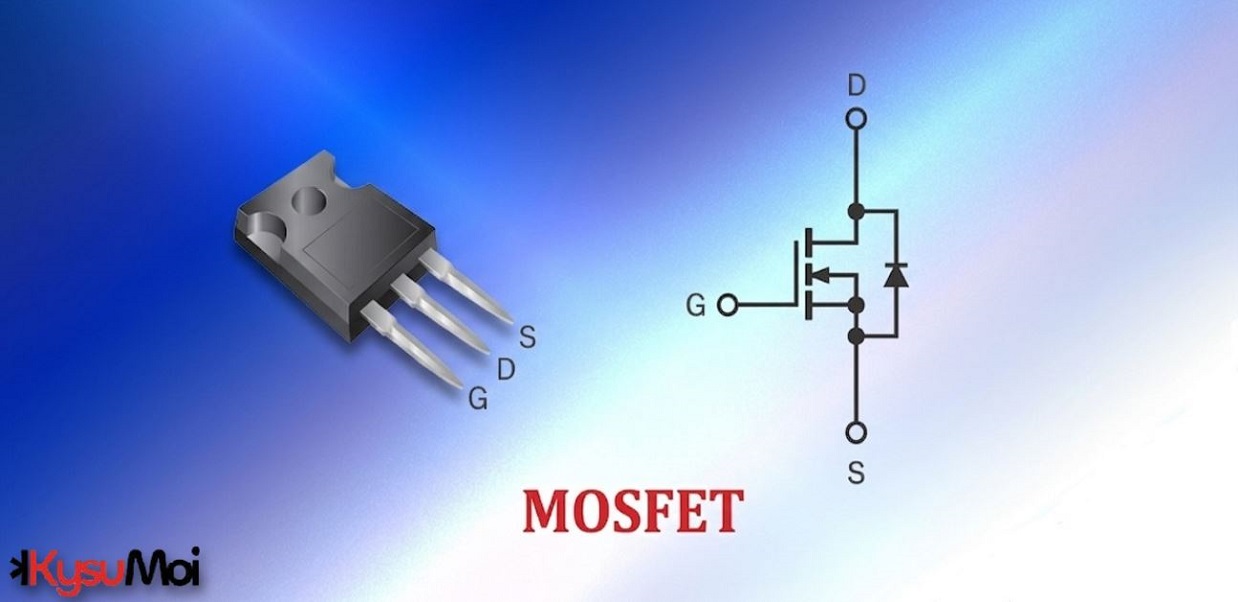

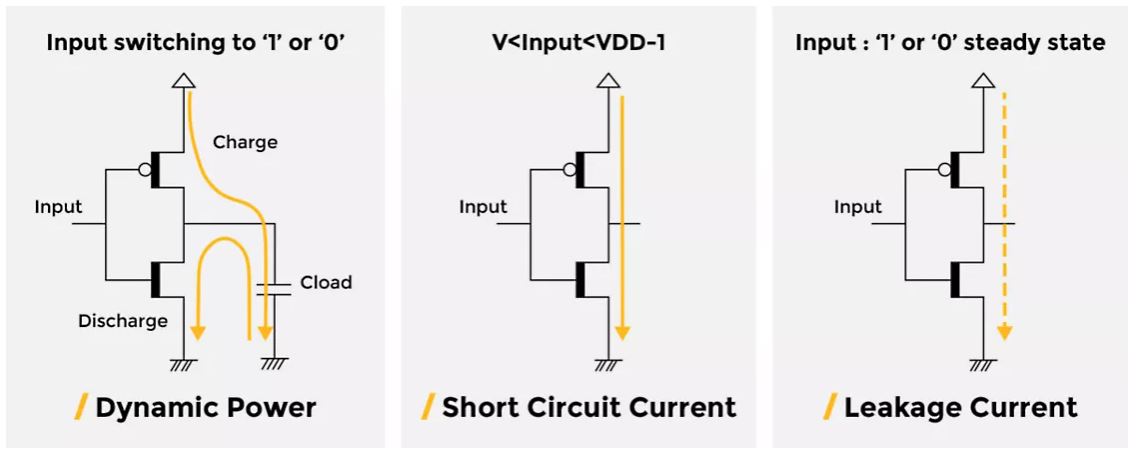

Thiết kế IC (mạch tích hợp) công suất thấp là một khía cạnh quan trọng của điện tử hiện đại, vì nó cho phép kéo dài tuổi thọ pin và giảm mức tiêu thụ năng lượng trong các thiết bị. Thị trường thiết bị chạy bằng pin ngày càng phát triển đã buộc các nhà thiết kế chip phải cân nhắc kỹ lưỡng các kỹ thuật khác nhau để giảm mức tiêu thụ điện năng của IC. Có một số kỹ thuật có thể được sử dụng để giảm mức tiêu thụ điện năng tĩnh và động của IC. Dòng điện một chiều và dòng điện rò rỉ là nguồn gốc của công suất tĩnh, trong khi công suất động phụ thuộc vào tần số, đến từ việc đóng cắt transistor và công suất ngắn mạch.

Để tạo ra một thiết kế tiết kiệm điện năng, nhà thiết kế phải giảm thiểu từng thành phần công suất riêng lẻ góp phần vào tổng mức tiêu thụ điện năng. Hình 1 cho thấy cả đặc tính công suất động và tĩnh. Việc sạc động của bộ biến tần bán dẫn kim loại-ôxít-ôxít bổ sung (CMOS) khiến mức tiêu thụ điện năng tỷ lệ thuận với tần số xung nhịp. Rò rỉ điện năng qua các transistor khi không hoạt động được coi là công suất tĩnh.

Nhà thiết kế công suất thấp có thể giảm tổng mức tiêu thụ điện năng bằng cách kiểm soát điện áp cung cấp, giảm độ phức tạp của mạch và tần số xung nhịp, đồng thời giám sát nguồn dòng điện một chiều và điện dung của các nút chuyển mạch. Mọi thứ đều được kết nối, vì vậy nhà thiết kế phải cân nhắc giữa các yếu tố này bằng cách thử nghiệm và sử dụng các kỹ thuật thiết kế công suất thấp để tối ưu hóa hiệu suất thiết kế.

Kỹ thuật và Thực hành Tốt nhất cho Thiết kế Công suất Thấp

Cổng đồng hồ

Một cách để giảm mức tiêu thụ điện năng của thiết bị là điều chỉnh thiết kế ở cấp độ chuyển đổi thanh ghi (RTL) . Đây là một trong những kỹ thuật phổ biến nhất để giảm mức tiêu thụ điện năng động. Ở cấp độ RTL, điện năng được tiêu thụ khi transistor thay đổi trạng thái logic hoặc khi điện năng được sử dụng để sạc điện dung tải. Tổng công suất động là:

trong đó CL là điện dung tải, C là điện dung bên trong chip, f là tần số hoạt động và N là số bit đang chuyển mạch. Có thể dễ dàng giảm dòng điện động bằng cách đóng ngắt xung nhịp khi không cần thiết. Thay vì sử dụng cổng AND/NOR, tốt hơn nên sử dụng cổng đóng ngắt xung nhịp dạng chốt để tránh tiêu thụ thêm điện năng. Việc tắt tín hiệu xung nhịp đến một số bộ phận nhất định của IC có thể giảm đáng kể mức tiêu thụ điện năng, vì các transistor trong những khu vực đó sẽ không đóng ngắt và tiêu thụ điện năng.

Cổng điện

Không phải tất cả các khối đều hoạt động liên tục trong một IC; điều này phụ thuộc vào ứng dụng của chúng trong thiết bị. Không cần cấp nguồn cho một khối nếu nó không hoạt động trong một trường hợp cụ thể. Bằng cách tắt nguồn cấp cho các khối không hoạt động, mức tiêu thụ điện năng có thể được giảm xuống. Để sử dụng hiệu quả kỹ thuật này, các nhà thiết kế có thể sử dụng các khối cách ly để ngăn chặn các tín hiệu không cần thiết đến từ các khối có cổng nguồn.

Cổng tần số

Như chúng ta đã biết, chip bao gồm nhiều khối, và mỗi khối không yêu cầu tần số cao nhất có thể để hoạt động. Kỹ thuật tốt nhất có thể là phân tách các khối dựa trên yêu cầu tần số của chúng và cung cấp tín hiệu xung nhịp khác nhau cho mỗi khối. Phương pháp này có thể giảm đáng kể mức tiêu thụ điện năng động cục bộ của IC.

Thiết kế đa điện áp

Không có khối nào trong thiết kế yêu cầu cùng một lượng điện năng để hoạt động. Bạn có thể phân vùng chip tùy thuộc vào hiệu suất của khối và yêu cầu điện áp của nó. Yêu cầu điện áp càng cao, mức tiêu thụ càng cao. Bằng cách tạo ra các đảo điện áp với các đầu vào điện áp khác nhau, việc giảm tổng mức tiêu thụ điện năng của một IC trở nên dễ dàng.

Tỷ lệ điện áp và tần số động

Kỹ thuật đảo điện áp có một hạn chế — một khi nguồn điện áp cung cấp cho một khối đã được thiết kế, nó không thể thay đổi sau này. Kỹ thuật điều chỉnh điện áp động cho phép nhà thiết kế linh hoạt thay đổi điện áp sau này theo yêu cầu. Nhà thiết kế có thể lập trình bộ điều chỉnh để thay đổi nguồn điện cho các khối khác nhau tùy theo dòng điện thay đổi. Tương tự, điều chỉnh điện áp có thể được kết hợp với điều chỉnh tần số, cho phép nhà thiết kế sửa đổi tín hiệu xung nhịp cung cấp cho từng khối với sự trợ giúp của một chương trình phần mềm.

Giảm công suất

Kỹ thuật giảm công suất quan trọng nhất cho đến nay là hạ thấp điện áp cung cấp của chip. Công suất chuyển mạch động chiếm ưu thế trong thiết kế finFET và tỷ lệ thuận với bình phương điện áp cung cấp, do đó thúc đẩy mạnh mẽ các quy trình điện áp cực thấp (ULV).

Đánh đổi điện năng rò rỉ

Công suất rò rỉ là một yếu tố tiêu hao năng lượng quan trọng trong các công nghệ tiền finFET và được kiểm soát tốt nhất bằng các thư viện đa Vt. Các thư viện này cung cấp hai hoặc ba phiên bản cho mỗi cell, mỗi phiên bản có một sự đánh đổi hiệu suất/rò rỉ khác nhau. Điều này cho phép các nhà thiết kế sử dụng các cell nhanh, rò rỉ trong việc định thời các đường dẫn quan trọng và sử dụng các cell chậm hơn, rò rỉ thấp trong các đường dẫn ít quan trọng hơn.

Nhìn chung, có nhiều kỹ thuật có thể được sử dụng để giảm mức tiêu thụ điện năng của IC. Bằng cách triển khai các kỹ thuật này và sử dụng các công cụ thiết kế và mô phỏng phù hợp, các nhà thiết kế có thể vượt qua những thách thức này. Các công cụ như Ansys RedHawk-SC cho phép các kỹ sư mô phỏng và dự đoán hành vi thiết kế ở mọi giai đoạn thiết kế, cho phép bạn thiết kế các IC công suất thấp, tiết kiệm năng lượng hơn và có tuổi thọ pin dài hơn.

Những thách thức trong thiết kế công suất thấp

- Biên độ sụt áp trở nên rất hẹp, đặc biệt là với các thiết kế điện áp cực thấp. Sự phát triển này đã khiến việc xác nhận sụt áp (IR) trở thành một phần thiết yếu của mọi thiết kế IC hiện đại.

- Điện áp cung cấp thấp khiến thời gian đường truyền dễ bị ảnh hưởng bởi sụt áp động (DVD). Ngoài ra, việc phân tích DVD với phạm vi phủ sóng đủ rộng để nắm bắt tất cả các tình huống chuyển mạch có thể xảy ra là rất khó khăn. Việc phân tích sụt áp cẩn thận là rất quan trọng để giảm thiểu tác động của DVD lên thời gian và tránh mất tần số do sụt áp IR bất ngờ.

- Các vùng đa điện áp cần được quản lý cẩn thận để đảm bảo chuyển đổi tín hiệu phù hợp và tính toàn vẹn của tín hiệu giữa các vùng điện áp khác nhau. UPF là một tiêu chuẩn được thiết kế để giúp giải quyết thách thức này.

- Cổng nguồn tạo ra hiện tượng chuyển đổi đầy thách thức — cả về điện và logic — khi bật lại một khối.

- Việc kiểm soát xung nhịp hiệu quả nhất khi được triển khai càng gần gốc của mạng phân phối xung nhịp càng tốt, nhưng điều này bị hạn chế bởi tính khả thi của việc định thời tín hiệu kích hoạt nếu nó đến đúng lúc. Điều này dẫn đến sự đánh đổi giữa hiệu suất năng lượng đạt được và nỗ lực tối ưu hóa thiết kế.

Tính hợp lệ của bất kỳ phân tích công suất nào đều phụ thuộc rất nhiều vào hoạt động của mạch. Tuy nhiên, việc tạo ra một kịch bản hoạt động thực tế và mang tính đại diện, nắm bắt được toàn bộ các chế độ công suất khả thi trong sử dụng thực tế ở tất cả các chế độ, không phải là điều dễ dàng. Một sai lầm phổ biến là sử dụng các vectơ hoạt động xác minh chức năng để tính toán công suất; những vectơ này gây hiểu lầm và không liên quan đến phân tích công suất. Các vectơ hoạt động tốt có thể được tạo thủ công, tự động bằng công cụ điện ("không vectơ"), hoặc bằng trình giả lập phần cứng chạy các ứng dụng thực tế.