Thiết kế mạng đồng hồ tốt hơn

Bài viết này khẳng định rằng công suất, hiệu suất và thời gian tối ưu phụ thuộc vào kiến trúc mạng đồng hồ.

Việc xây dựng nền tảng kiến trúc mạng xung nhịp phù hợp sẽ tạo nên sự khác biệt lớn cho hiệu suất, công suất và thời gian hoạt động tốt nhất của chip, đặc biệt là trong các SoC nút tiên tiến chứa hàng tỷ bóng bán dẫn.

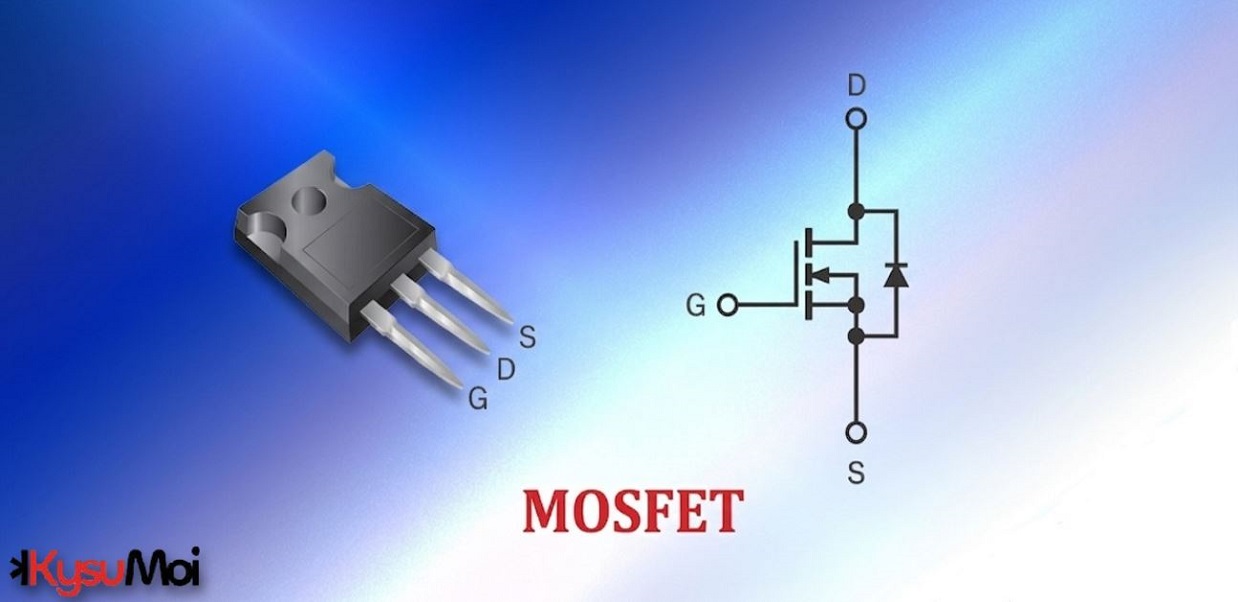

Mỗi bóng bán dẫn, hoạt động như một cell chuẩn, cần một xung nhịp. Một mạng xung nhịp hiệu quả sẽ đảm bảo các bóng bán dẫn chuyển mạch tiết kiệm điện năng. Trong các nút tiên tiến ngày nay, khi một thiết kế chuyển từ N5 sang N3, xưởng đúc đảm bảo thiết kế đó tiết kiệm điện năng khi chuyển mạch, giúp kỹ sư thiết kế không phải can thiệp vào quá trình này.

Nhưng hiệu suất thậm chí còn có thể được cải thiện hơn nữa thông qua việc mở rộng quy trình bằng cách điều chỉnh xung nhịp và định tuyến xung nhịp. Bằng cách loại bỏ một số bộ đệm hoặc định cỡ chúng khác nhau, thế hệ tiếp theo có thể tiết kiệm nhiều điện năng hơn. Điều này cũng cho phép có nhiều tùy chọn tối ưu hóa năng lượng hơn.

Điều quan trọng là phải nắm bắt được các biến thiên công suất do xung nhịp gây ra. Thông thường, biến thiên công suất xảy ra trong thiết kế khi xung nhịp được đóng hoặc không đóng, và biến thiên công suất là một hiện tượng ngẫu nhiên của sơ đồ xung nhịp.

Nhưng khi mạng lưới đồng hồ trải rộng trên một con chip có kích thước bằng lưới, việc đóng thời gian trở nên phức tạp hơn theo cấp số nhân, đặc biệt là đối với các hệ thống đồng bộ lớn. Các nhà thiết kế phải đối mặt với những thách thức to lớn khi việc duy trì độ lệch đồng hồ trở nên khó khăn hơn và biên độ thời gian bị thu hẹp.

Tệ hơn nữa, mạng xung nhịp tiêu thụ điện năng với tốc độ chóng mặt. Jeffrey Fredenburg, Giám đốc Công nghệ kiêm đồng sáng lập Movellus, cho biết: "Mạng xung nhịp có thể tiêu thụ tới một nửa công suất động của chip và dẫn đến tăng chi phí hệ thống, giảm phạm vi công suất ở cấp độ hệ thống và tăng tổng chi phí sở hữu cho các nhà sản xuất thiết bị gốc (OEM) AI, trung tâm dữ liệu và ô tô " .

Theo truyền thống, việc lựa chọn cấu trúc mạng đồng hồ và chiến lược là một quyết định thiết kế vật lý. "Tuy nhiên, các trung tâm thiết kế đang áp dụng chỉ thị dịch chuyển sang trái với kiến trúc đồng hồ của họ và đưa quyết định đến gần hơn với giai đoạn kiến trúc. Bằng cách dịch chuyển sang trái, các nhà thiết kế có thể khai thác hiệu suất năng lượng và hiệu suất vượt trội hơn trong giai đoạn xây dựng (đặt và định tuyến)", Fredenburg nói.

Trước đây, các nhóm kỹ sư đã tạo ra một cây đồng hồ phức tạp để chỉ ra rằng họ muốn mọi thứ trên chip, từ góc này sang góc kia, phải đồng bộ. "Thách thức là họ phải có một đồng hồ ở đâu đó gần trung tâm chip, và sau đó phân phối đồng hồ đó theo cách mà bất kỳ mạch nào trên chip luôn đồng bộ với các mạch khác", Steven Woo, đồng nghiệp và nhà phát minh lỗi lạc tại Rambus , cho biết . "Tuy nhiên, việc đồng bộ hóa toàn cục này trở thành một vấn đề vì việc phân phối đồng hồ tần số cao trên toàn bộ chip tiêu tốn rất nhiều năng lượng. Sau đó, mọi người bắt đầu nói rằng, 'Có lẽ tôi không cần phải đồng bộ hóa mọi thứ trên toàn cục. Có lẽ chỉ trong một vài phần nhỏ trong thiết kế chip của mình, tôi có thể đồng bộ hóa cục bộ các mạch.' Nhưng sau đó lại nảy sinh vấn đề giao thoa miền khi chuyển sang miền khác, và cần có các mạch đặc biệt để cho phép dữ liệu được truyền giữa các ranh giới không đồng bộ với xung nhịp. Nhìn vào các công ty thiết kế chip AI, điều họ làm là nói rằng, 'Có lẽ tôi thậm chí không cần phải có các đảo đồng bộ hóa lớn. Có lẽ tôi chỉ cần đồng bộ với các mạch lân cận ngay bên cạnh mình.' Điều đó làm giảm nhu cầu phân bổ đồng hồ có độ chính xác cao trên toàn bộ chip.”

Điều này không có nghĩa là chúng ta sẽ thấy những thiết kế không có đồng hồ. "Đồng hồ vẫn cần thiết, nhưng yêu cầu đồng bộ tất cả chúng trên toàn bộ chip sẽ giảm đi", Woo nói. "Sau đó, bạn cũng có thể bắt đầu giảm lượng điện năng tiêu thụ. Một số chip AI này, và những thứ như mảng tâm thu, không nhất thiết cần đến cây đồng hồ toàn cục khổng lồ vốn ngốn rất nhiều điện năng. Đó là lúc bạn cần tận dụng tất cả năng lượng đó và chuyển đổi chúng thành những thứ như nhiều SRAM và nhiều thành phần tính toán hơn."

Nguyên nhân/kết quả

Nhưng nếu các đồng hồ không đồng bộ, sẽ có tác động. "Về mặt hiệu suất, sẽ mất một chút thời gian để vượt qua những ranh giới này vì chúng không hoàn toàn đồng bộ và bạn phải chấp nhận điều đó", ông nói. "Trong trường hợp của các nhà phát triển AI, họ nói, 'Chúng tôi sẽ giải quyết loại vấn đề đó vì điều chúng tôi quan tâm là thông lượng toàn cầu. Nếu tôi có thể chứng minh rằng với việc tiết kiệm điện năng, tôi có thể có nhiều công cụ tính toán hơn, mặc dù có thể mất nhiều thời gian hơn một chút để truyền dữ liệu, tôi có thể có nhiều đường ống tính toán hơn và cuộc sống của tôi sẽ tốt hơn nếu tôi làm được điều đó.' Về mặt điện năng, bạn tiết kiệm được điện năng phân phối đồng hồ, vì vậy điều đó có xu hướng tốt, nhưng độ trễ để đưa mọi thứ qua chip có xu hướng cao hơn. Vì vậy, nếu bạn đang ở trong một ứng dụng rất quan trọng về độ trễ, nói chung, bạn muốn có nhiều mạch đồng bộ hơn và vượt qua ranh giới đồng bộ hơn. Nhưng nếu bạn sẵn sàng từ bỏ một số thứ đó, thì việc chuyển khỏi loại kiến trúc đó là rất hợp lý."

Biến thể tạo thêm một nếp nhăn nữa, vì bất kỳ biến thể nào về công suất đều ảnh hưởng đến thời gian. "Cũng giống như bạn có gợn sóng điện chạy qua chip của mình, hiệu suất gợn sóng cũng theo cách tương tự khi điện áp giảm trên ô nhớ", Marc Swinnen, giám đốc tiếp thị sản phẩm tại Ansys cho biết . "Nó vẫn có thể nằm trong giới hạn cho phép của mức sụt điện áp, nhưng điều đó có nghĩa là ô nhớ chậm hơn một chút. Điện áp cung cấp càng thấp, chuyển mạch bóng bán dẫn càng chậm. Vì vậy, khi điện áp của bạn giảm, hiệu suất của bạn cũng giảm theo. Và nếu bạn có đủ độ sụt cục bộ, mỗi độ sụt có thể ổn theo cách riêng của nó. Nhưng khi kết hợp lại, chúng sẽ chạm đến con đường quan trọng này và con đường này hiện quá chậm hoặc quá nhanh. Nếu điện áp tăng đột biến, bạn có thể có hiệu suất nhanh hơn và bạn có thể bỏ lỡ thời gian giữ. Vấn đề là tác động của nhiễu công suất đến thời gian và nạn nhân chính của điều này là xung nhịp."

Đồng hồ là một mạng lưới lớn, và lý tưởng nhất là có một luồng xung rất đều đặn đi xuống cây đồng hồ. Tuy nhiên, do việc chuyển mạch gần đồng hồ, các cổng truyền đồng hồ này sẽ ngẫu nhiên chậm lại hoặc tăng tốc một chút, và điều đó gây ra hiện tượng dao động đồng hồ. Một trong những thành phần chính của dao động đồng hồ hiện nay là gợn sóng công suất và biến thiên công suất.

Swinnen cho biết: "Bất kỳ mạch điện tử nào ngày nay về cơ bản đều là một máy trạng thái, trong đó đồng hồ sẽ chuyển từ trạng thái này sang trạng thái khác và khoảng thời gian giữa hai lần đồng hồ, về cơ bản là lượng công việc bạn có thể hoàn thành trong bất kỳ pha đồng hồ nào". “Nhưng bạn phải có biên độ. Tất nhiên, có thời gian thiết lập và giữ, làm giảm xung nhịp của bạn, nhưng jitter lại là một biến động hoặc ẩn số khác làm thu hẹp thời gian bạn phải làm việc, bởi vì xung nhịp có thể trễ hoặc sớm. Nó là ngẫu nhiên. Cách thức jitter được thống kê, vì vậy nó ảnh hưởng đến toàn bộ thời gian của chip. Nếu bạn có thể giảm jitter xuống, giả sử, 10%, hoặc ít nhất là dự đoán nó tốt hơn, thì cũng giống như có được xung nhịp nhanh hơn 10%, điều này có tác động rất lớn. Việc biên độ ngày càng khó thực hiện hơn nhiều trong thời đại ngày nay, vì vậy bạn cần độ chính xác. Tuy nhiên, nguyên nhân chính của jitter là sự thay đổi công suất, đó là lúc phân tích jitter xung nhịp phát huy tác dụng. Các công cụ tính thời gian truyền thống coi điện áp là một thứ cố định. Tất cả chúng đều được xây dựng với giả định điện áp cố định, vì vậy chúng không có vị trí tốt để xử lý vấn đề này, bởi vì ngay từ đầu chúng không thấy sự thay đổi công suất. Đó không phải là một trong những thông số của chúng.”

Hơn nữa, tại các nút quy trình rất tiên tiến, hiệu ứng không khớp gây ra hiện tượng nhiễu.

Priyank Shukla, giám đốc tiếp thị sản phẩm cấp cao tại Synopsys cho biết: “Việc ghép nối các bóng bán dẫn là lợi thế chính của công nghệ quy trình tiên tiến ở chỗ bạn có thể có hai bóng bán dẫn được ghép nối rất, rất chặt chẽ với nhau, do đó nếu diện tích lớn hơn, độ không khớp sẽ nhỏ hơn”. “ Khi địa lý thu hẹp lại, bạn không chỉ có các hệ số hình thức nhỏ hơn mà còn có finFET. Trước đây chúng tôi có dạng phẳng, vì vậy việc ghép nối dễ dàng hơn. Trong finFET, có ba vây để thực hiện một bóng bán dẫn và các bước quy trình đã được thêm vào để thực hiện các vây đó. Vì vậy, sự không khớp đã thể hiện ở các loại jitter khác nhau, đây là một điều mới. Trước đây không có hiện tượng này. Ngoài ra, trước đây, kỹ thuật tiêu chuẩn là tăng kích thước. Nhưng bây giờ, nhìn chung nó không giúp ích gì, vì nó làm tăng điện dung nếu diện tích lớn hơn. Bạn đang thêm điện dung, vì vậy cần có mạch mới để giải quyết những thách thức này. Đây là một điểm mới liên quan đến các nút nâng cao.”

Đối với các nhà thiết kế kỹ thuật số, các công cụ thương mại có thể giải quyết vấn đề này một cách trực tiếp, từ phân tích độ trễ xung nhịp (clock jitter) đến phân tích thời gian thống kê dựa trên biến thiên. Các công cụ này có thể được sử dụng để phân tích ảnh hưởng của điện áp và nhiễu điện áp lên thời gian, đồng thời có thể tính toán độ trễ xung nhịp, cho biết độ trễ sẽ là bao nhiêu và nguyên nhân gây ra độ trễ đó.

Các kỹ thuật khác bao gồm phân tích sụt áp động, để xem những gì đang chuyển mạch trong vùng lân cận. Điều này cho phép nhóm thiết kế tăng cường mạng xung nhịp để giảm độ nhạy với nhiễu điện áp mà không phải trả giá trên toàn bộ chip, hoặc thậm chí trên toàn bộ mạng xung nhịp. Có những giai đoạn cụ thể sẽ bị ảnh hưởng nhiều hơn bởi nhiễu điện áp, vì vậy có thể thực hiện phân tích nguyên nhân gốc rễ, sau đó nhắm mục tiêu, sửa chữa triệt để và đệm xung nhịp để giảm độ nhạy. Cách tiếp cận chi tiết này giúp hạn chế biên độ vì nó không giả định trường hợp xấu nhất ở mọi nơi.

“Đồng hồ thường bị bỏ qua, nhưng mọi người quên rằng trong các chip tốc độ cao, 30% đến 50% toàn bộ năng lượng trong chip được tiêu thụ chỉ riêng cho đồng hồ,” Swinnen nói. “Một phần ba đến một nửa năng lượng bị đốt cháy trong mạng đồng hồ. Vì vậy, khi bạn thiết kế công suất thấp, đó là điều đầu tiên bạn nên xem xét.”

Tín hiệu tương tự/hỗn hợp

Đối với các kỹ sư analog, không có công cụ nào để xử lý đồng hồ theo cùng một cách, vì vậy rất nhiều thứ được học trong ngành. "Các kỹ sư analog không được dạy những điều này vì các nút quy trình finFET tiên tiến rất hiếm khi được dạy", Shukla nói. "Nhưng trong công việc, tất cả các chip tiên tiến đều nằm trong quy trình finFET, vì vậy các kỹ sư analog học được điều này trong ngành. Họ học cách thiết kế tốt hơn thông qua các bài báo của IEEE hoặc rất nhiều hội thảo trực tuyến."

Mặc dù có các công cụ, nhưng liệu điều này có nghĩa là các vấn đề về kiến trúc mạng đồng hồ và tác động của chúng đến nguồn điện đã được giải quyết hay không?

Rambus' Woo không nghĩ vậy. “Tôi không nghĩ ai cũng hài lòng. Ai cũng muốn công suất thấp hơn, đặc biệt là để tạo xung nhịp. Trong một số mạch PHY của chúng tôi, chúng tôi có các xung nhịp phải phân phối trên khoảng cách xa, và việc phân phối xung nhịp tần số cao trên khoảng cách xa là một thách thức. Phải có bộ lặp và những thứ tương tự, nên không ai hài lòng với điều đó. Liệu đây có phải là một vấn đề đã được giải quyết? Nó giống như mọi thứ trong thiết kế chip — đó là một vấn đề mà mọi người có thể giải quyết ngay bây giờ. Rồi đến một lúc nào đó, họ không thể giải quyết được nữa, và khi đó bạn thực sự phải làm gì đó. Đó là vấn đề Đập Chuột Chũi, khi có một con chuột chũi khác mà bạn phải đập trước. Cũng giống như khi một con chuột chũi nhô đầu lên, thì bạn phải xử lý con đó. Phần lớn việc này chỉ là cố gắng giữ mọi thứ ở mức mà không có thứ nào nhô ra nhiều hơn thứ khác. Hiện tại đã có giải pháp, nhưng công suất xung nhịp luôn là một vấn đề. Câu hỏi đặt ra là khi nào bạn thực sự buộc phải giải quyết nó tiếp theo.”

Những người khác cũng nêu lên những lo ngại tương tự. "Khi chúng ta có những kiến trúc trong đó có sự phụ thuộc dữ liệu giữa các lớp tính toán khác nhau, chúng ta cần đảm bảo rằng có một số loại đồng bộ hóa trong toàn bộ đường dẫn dữ liệu", Ramesh Chettuvetty, tổng giám đốc giải pháp bộ nhớ tại Infineon Technologies cho biết . "Thứ hai, khi kích thước chip tăng lên, như trong RAM nhúng và đa lõi, chúng ta đang nói về đế 100 mm² hoặc đế 800 mm². Đảm bảo rằng chúng ta có đồng bộ hóa ở bốn góc của chính con chip sẽ là một thách thức vì chắc chắn sẽ có độ trễ định tuyến xung nhịp trong chính con chip. Để giải quyết tất cả những điều đó, chúng ta sẽ cần có một kiến trúc xung nhịp rất chắc chắn, có tính đến tất cả các yêu cầu về thiết lập và thời gian giữ. Và đây là những xung nhịp tần số cao, vì vậy bạn chắc chắn sẽ cần một số loại mạng đồng bộ hóa giữa các lõi khác nhau. Một cách khác để chúng ta có thể thực hiện theo cách đồng bộ là dựa vào bắt tay giữa các lõi. Vấn đề với cách tiếp cận đó là nó làm giảm hiệu quả di chuyển dữ liệu."

Đặc biệt trong các ứng dụng tính toán trong bộ nhớ, thách thức lớn nhất mà mọi người phải đối mặt trong các kiến trúc này là cải thiện hiệu quả luồng dữ liệu.

Chettuvetty cho biết: “Ngay khi chúng ta có một giao thức bắt tay hoặc mạch trọng tài dựa trên giao tiếp qua lại, nó sẽ làm chậm quá trình di chuyển dữ liệu giữa các lớp, điều này không tốt trong các kiến trúc này”. “Nó sẽ làm giảm hiệu quả đáng kể. Các nhóm kỹ thuật dựa vào việc sử dụng các kiến trúc đồng bộ càng nhiều càng tốt, nhưng là kiến trúc đồng bộ mà không có bất kỳ nút thắt nào trong luồng dữ liệu. Đó là điều mà mọi người đang hướng tới. Mức độ thành công của chúng sẽ quyết định hiệu quả năng lượng tổng thể của hệ thống. Đó là một khía cạnh rất quan trọng. Kiến trúc xung nhịp là một khía cạnh rất quan trọng trong các hệ thống này. Đây là các thông lệ tiêu chuẩn mà các nhóm kỹ thuật sử dụng trong nhiều SoC này và họ nắm bắt khá rõ cách thực hiện. Tôi không thấy một cách tiếp cận hoàn toàn đổi mới nào trong các kiến trúc xung nhịp dành riêng cho AI, nhưng hiệu quả luồng dữ liệu và kiến trúc đồng bộ là những gì mọi người đang tìm kiếm để cải thiện hiệu quả nói chung, điều này rõ ràng có nghĩa là xung nhịp có một vị trí quan trọng.”

Kết luận

Fredenburg của Movellus cho biết mạng đồng hồ là một trong những mạng lớn nhất trên chip, và chúng có tác động lớn đến công suất, hiệu suất và diện tích. "Với mỗi cấu trúc mạng đồng hồ, các nhà thiết kế phải cân nhắc những yếu tố quan trọng, chẳng hạn như công suất cho hiệu suất hoặc thời gian đưa sản phẩm ra thị trường cho hiệu suất."

Trong khi cấu trúc đồng hồ vẫn tương đối ổn định trong 25 năm qua, các cấu trúc mới đang xuất hiện, mang lại bước nhảy vọt đáng kể về hiệu suất năng lượng và tính linh hoạt trong việc đóng thời gian.