Nhiều thiết bị điện được thiết kế để hoạt động với điện áp cung cấp thấp, nhưng chúng vẫn cần một điện áp tối thiểu để hoạt động chính xác. Điều này đặc biệt quan trọng trong các ứng dụng dùng pin, nơi điện áp khả dụng giảm khi pin xả. Khi điện áp nguồn trở nên quá thấp, một số vấn đề có thể phát sinh, bao gồm:

- Tham chiếu dải cấm có thể tạo ra điện áp không chính xác

- Các hàm logic có thể tạo ra các tín hiệu điều khiển không chính xác

- Transistor công suất có thể chỉ bật hoặc tắt một phần

Chức năng khóa điện áp thấp (UVLO) đảm bảo thiết bị vẫn không hoạt động cho đến khi điện áp nguồn đủ cao để đảm bảo hoạt động ổn định, dẫn đến hiệu suất hệ thống đáng tin cậy hơn.

Mục đích

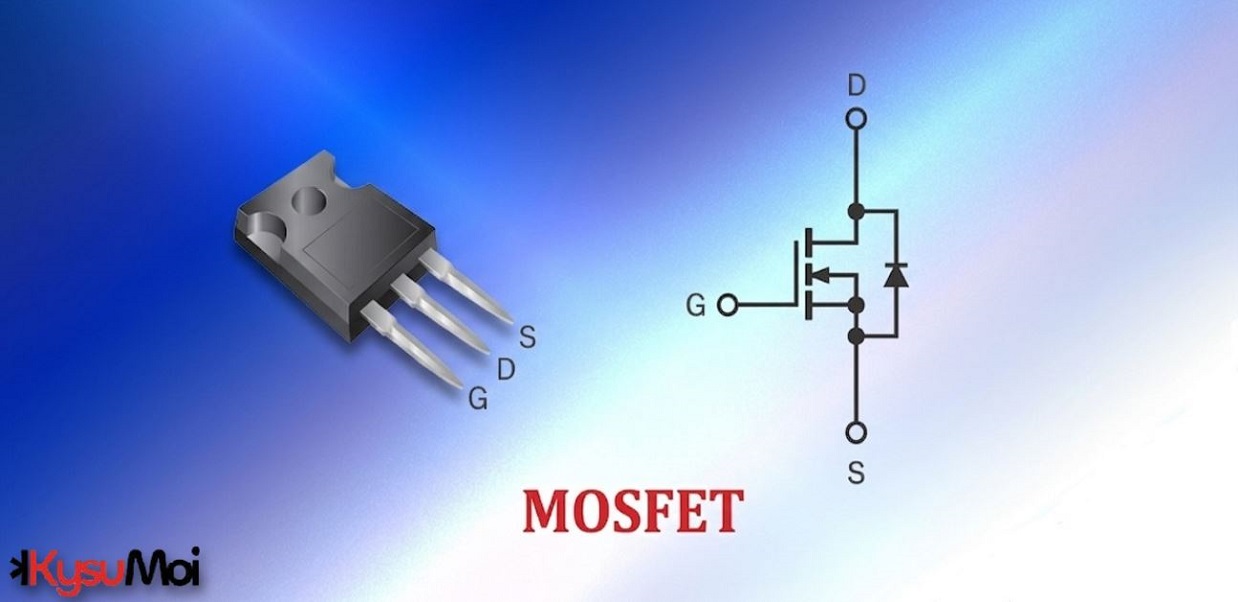

Mục tiêu của mạch UVLO là phát hiện khi điện áp nguồn không đủ và "khóa" thiết bị, đảm bảo thiết bị vẫn ở trạng thái ổn định cho đến khi điện áp đủ lại. Trong mạch này, điện áp nguồn được đo bằng bộ chia điện trở và so sánh với một điện áp ngưỡng cố định (VT). Nếu điện áp phân chia thấp hơn ngưỡng, đầu ra của bộ so sánh sẽ thay đổi và vô hiệu hóa các mạch phía sau bằng cách mở một công tắc. Thực tế, việc "mở công tắc" thường có nghĩa là đưa MOSFET vào trạng thái không dẫn điện.

Vì mạch này được thiết kế để phát hiện các điện áp nguồn có thể gây sự cố cho các phần khác của hệ thống, nhà thiết kế cần đảm bảo rằng bộ tạo điện áp ngưỡng và bộ so sánh có thể hoạt động bình thường ở các điện áp nguồn thấp này. Thông thường, bộ so sánh trong mạch UVLO sẽ có tính năng trễ để ngăn việc bật và tắt nguồn hệ thống liên tục khi điện áp nguồn gần đạt ngưỡng.

Các chế độ hoạt động

1. Tắt

Khi điện áp nguồn dưới ngưỡng UVLO, thiết bị sẽ tắt (được biểu thị bằng các vùng màu đỏ). Tất cả các khối bên trong, ngoại trừ mạch UVLO, đều bị vô hiệu hóa. Dòng cung cấp đầu vào khi thiết bị tắt thường rất nhỏ.

2. Chức năng

Khi điện áp cung cấp trên ngưỡng UVLO tối đa nhưng dưới điện áp hoạt động tối thiểu được khuyến nghị (được biểu thị bằng các vùng màu vàng), tất cả các chức năng của thiết bị đều được bật, nhưng hiệu suất đầy đủ không được chỉ định. Ví dụ, một bộ chuyển đổi DC/DC hoạt động trong vùng này có thể điều chỉnh chính xác nhưng có thể không cung cấp được dòng điện đầu ra tối đa của nó.

3. Hiệu suất đầy đủ

Hiệu suất đầy đủ chỉ được chỉ định nếu điện áp cung cấp nằm trong điều kiện hoạt động được khuyến nghị (được hiển thị bằng vùng màu xanh lá cây).

Trong các ứng dụng quan trọng như tàu vũ trụ, ngưỡng UVLO thường cao hơn điện áp hoạt động tối thiểu mà hệ thống đạt được hiệu suất tối đa. Các hệ thống như vậy cực kỳ bền bỉ, nhưng chúng không hiệu quả về chi phí đối với hầu hết các ứng dụng thương mại, vì các thành phần được thiết kế quá mức cho phần lớn các trường hợp sử dụng.

4. Không xác định

Ngưỡng UVLO được chỉ định với dung sai nhất định để cho phép các biến thể về quy trình và nhiệt độ. Do đó, có một dải điện áp cung cấp (vùng màu xám) mà người dùng không thể chắc chắn thiết bị có hoạt động hay không. Điều này không có nghĩa là hành vi của thiết bị hoàn toàn không thể đoán trước. Điều đó có nghĩa là thiết bị đang tắt hoặc đang hoạt động, nhưng trạng thái nào trong hai trạng thái này mà thiết bị đang hoạt động thì không được xác định rõ ràng vì nó phụ thuộc vào vị trí chính xác của ngưỡng UVLO trong vùng xám.

Chân chức năng UVLO

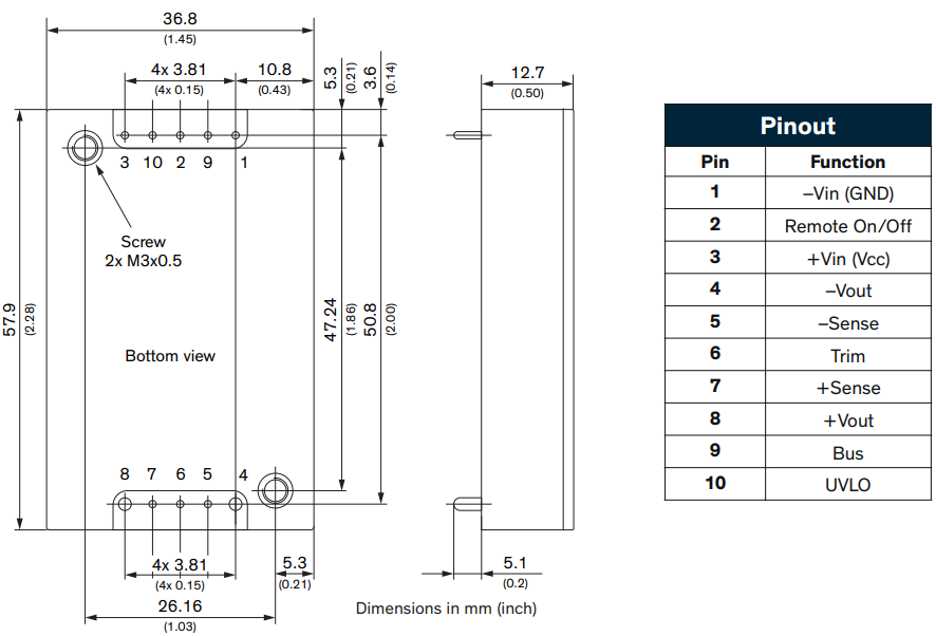

UVLO là một tính năng được tìm thấy trong một số bộ nguồn tích hợp và bộ điều chỉnh điện áp. Nếu bạn kiểm tra một mô-đun điều chỉnh điện áp và tham khảo sơ đồ chân trong bảng dữ liệu, bạn có thể nhận thấy một chân UVLO. Ví dụ, trong sơ đồ chân của bộ điều chỉnh nguồn dạng khối tứ phân cho viễn thông, các chân này được tiêu chuẩn hóa cao và bao gồm hai chân quan trọng cho mục đích bảo vệ và ổn định: UVLO và Bus. Trong trường hợp này, chân UVLO được chỉ định là chân 10 trong sơ đồ chân, mặc dù số chân không theo thứ tự đối với linh kiện cụ thể này.

Trong hình được đề cập ở trên, sơ đồ chân cho thấy cả chân UVLO và chân Bật/Tắt từ xa. Cái sau hoạt động như một chân EN (hoặc tương đương với chân SHDN), được dùng để bật hoặc tắt bộ điều chỉnh.

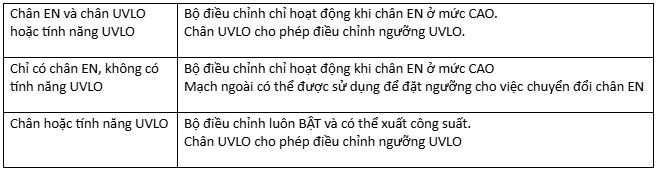

Một số bộ điều chỉnh điện có cả hai chân. Trong những trường hợp như vậy, chân UVLO đặt ngưỡng bật, nhưng chân EN phải được giữ BẬT (hoặc chân SHDN được giữ TẮT) để bộ điều chỉnh bật nguồn, bất kể ngưỡng chân UVLO là bao nhiêu. Nếu tính năng UVLO cố định và chân EN nằm trên cùng một gói, tính năng UVLO tích hợp vẫn sẽ hoạt động miễn là chân EN vẫn ở trạng thái BẬT.

Bảng dưới đây minh họa các tình huống khác nhau liên quan đến chân EN và chân UVLO hoặc tính năng UVLO tích hợp.

Như đã chỉ ra, các chân này cung cấp khả năng kiểm soát nhiều hơn đối với các chức năng của bộ điều chỉnh điện áp. Trong trường hợp các bộ điều chỉnh có dải điện áp đầu vào rộng, chẳng hạn như bộ chuyển đổi buck-boost đầu vào rộng, ngưỡng UVLO có thể được đặt ngay trên điểm giảm hiệu suất, thường là trên mức thấp của dải điện áp phân cực. Điều này đảm bảo bộ điều chỉnh luôn hoạt động trong phạm vi hiệu quả cao.

Một cách tiếp cận khác là sử dụng chân EN làm chân UVLO có trễ. Phương pháp này yêu cầu một mạch bổ sung với bộ so sánh. Bằng cách sử dụng nguồn điện áp tham chiếu, bộ so sánh đặt ngưỡng trên chân EN, sao cho EN chỉ ở mức CAO khi điện áp đầu vào trên ngưỡng, mô phỏng chức năng UVLO chỉ với một chân.

Hiện tượng trễ và "dao động" của UVLO

Các mạch UVLO thường được thiết kế với một số độ trễ. Khi một thiết bị được bật, dòng điện nó tiêu thụ có thể làm giảm điện áp nguồn. Không có hiện tượng trễ, sụt áp này có thể ngay lập tức tắt thiết bị trở lại. Điều này đặc biệt có vấn đề trong các hệ thống có trở kháng điện áp nguồn tương đối cao hoặc những hệ thống được cấp qua cáp dài. Trong một hệ thống được thiết kế tốt, độ sụt áp trong trường hợp xấu nhất do thiết bị bật lên nhỏ hơn độ trễ UVLO (với một chút dự phòng).

Tuy nhiên, trong các hệ thống có trở kháng điện áp nguồn cao, độ sụt xảy ra khi thiết bị bật (hoặc sự tăng đột ngột khi thiết bị tắt) có thể vượt quá độ trễ UVLO, khiến thiết bị bật và tắt lặp đi lặp lại trước khi ổn định ở trạng thái ổn định. Để giảm thiểu vấn đề này, có thể tăng độ trễ của UVLO. Tuy nhiên, việc tăng thêm độ trễ có nghĩa là tăng ngưỡng trên hoặc hạ ngưỡng dưới. Cái trước đòi hỏi điện áp cung cấp cao hơn để khởi động, trong khi cái sau thường làm tăng chi phí của thiết bị do cần các kỹ thuật tiên tiến hơn và bóng bán dẫn công suất lớn hơn. Cả hai lựa chọn đều không lý tưởng cho khách hàng, vì vậy mục tiêu là tìm ra sự cân bằng giữa chi phí và hiệu suất. Độ trễ UVLO vài trăm millivolt là điển hình cho các thiết bị nguồn của TI và thường đủ cho các hệ thống được thiết kế tốt với trở kháng điện áp cung cấp hợp lý.

Cũng đáng lưu ý rằng ngưỡng giảm của chức năng UVLO thường được xác định chính xác hơn ngưỡng tăng. Điều này là do tham chiếu dải cấm mà từ đó các ngưỡng UVLO được lấy ra hoạt động ở trạng thái chưa được điều chỉnh (kém chính xác hơn) cho đến khi thiết bị được bật. Sau khi thiết bị được bật, điện áp đầu ra của dải cấm sẽ được khởi tạo và trở nên hoàn toàn chính xác, giúp ngưỡng giảm chính xác hơn.

Cuối cùng, hiện tượng dội lại của UVLO nên được xem xét cả trong quá trình sản xuất và trong ứng dụng cuối cùng. Một số hệ thống hoạt động bình thường trong ứng dụng cuối cùng, nơi có kết nối ngắn, trở kháng thấp giữa pin và bảng mạch. Tuy nhiên, chúng có thể không khởi động đúng cách trong dây chuyền sản xuất, nơi sử dụng cáp dài (dài vài mét) để kết nối thiết bị với nguồn điện thử nghiệm.