Bộ cộng nhìn trước mang theo – Mạch, Bảng chân lý & Ứng dụng

Chúng ta hãy cùng tìm hiểu về Carry-Lookahead Adder: mạch điện, bảng chân lý và ứng dụng thực tế của nó.

Các loại hệ thống số khác nhau được xây dựng từ rất ít loại cấu hình mạng cơ bản như cổng AND, cổng NAND, cổng OR, v.v... Các mạch cơ bản này được sử dụng lặp đi lặp lại trong nhiều tổ hợp tôpô khác nhau. Ngoài việc thực hiện logic, hệ thống số còn phải lưu trữ số nhị phân. Các ô nhớ này, còn được gọi là FLIP-FLOP , được thiết kế để thực hiện một số chức năng như phép cộng nhị phân. Do đó, để thực hiện các chức năng đó, các tổ hợp cổng logic và FLIP-FLOP được thiết kế trên một IC đơn chip. Các IC này tạo thành các khối xây dựng thực tế của hệ thống số. Một trong những khối xây dựng như vậy được sử dụng cho phép cộng nhị phân là Bộ cộng nhìn trước Carry (Carry Look-ahead Adder).

Carry Look-ahead Adder là gì?

Một máy tính kỹ thuật số phải chứa các mạch có thể thực hiện các phép tính số học như cộng, trừ, nhân và chia. Trong đó, cộng và trừ là các phép tính cơ bản, còn nhân và chia là phép cộng và trừ lặp lại.

Để thực hiện các phép toán này, 'mạch cộng' được triển khai bằng cách sử dụng các cổng logic cơ bản. Mạch cộng được phát triển thành mạch bán cộng, mạch cộng toàn phần, mạch cộng gợn sóng và mạch cộng nhìn trước có mang.

Trong số đó, mạch cộng Carry Look-ahead là mạch cộng nhanh hơn. Nó giảm độ trễ lan truyền xảy ra trong quá trình cộng bằng cách sử dụng mạch phần cứng phức tạp hơn. Nó được thiết kế bằng cách biến đổi mạch cộng Ripple-carry sao cho logic nhớ của bộ cộng được chuyển thành logic hai cấp.

Bộ cộng nhìn trước 4 bit

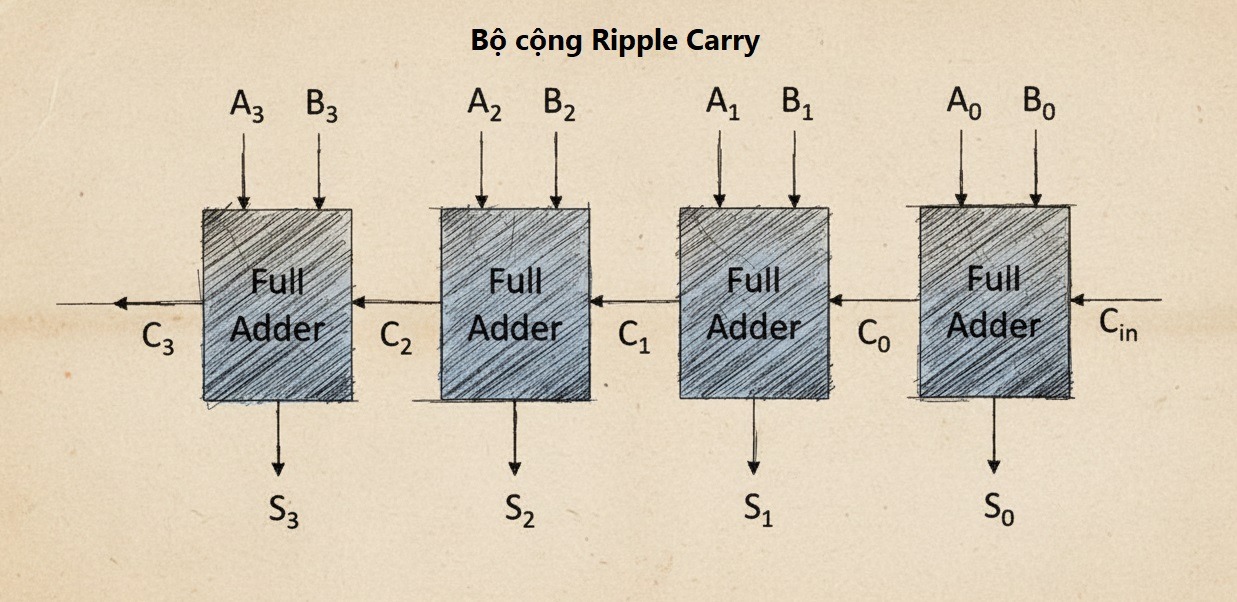

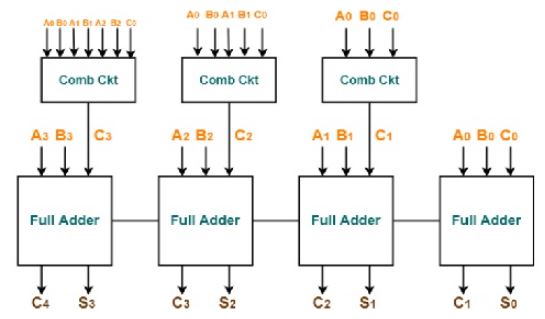

Trong các bộ cộng song song, đầu ra nhớ của mỗi bộ cộng đầy đủ được đưa vào làm đầu vào nhớ cho trạng thái bậc cao hơn tiếp theo. Do đó, các bộ cộng này không thể tạo ra đầu ra nhớ và tổng của bất kỳ trạng thái nào trừ khi có sẵn đầu vào nhớ cho trạng thái đó.

Vì vậy, để tính toán diễn ra, mạch phải đợi cho đến khi bit nhớ được truyền đến tất cả các trạng thái. Điều này gây ra độ trễ truyền bit nhớ trong mạch.

Hãy xem xét mạch cộng gợn sóng nhớ 4 bit ở trên. Ở đây, tổng S3 có thể được tính ngay khi các đầu vào A3 và B3 được cung cấp. Tuy nhiên, bit nhớ C3 không thể được tính toán cho đến khi bit nhớ C2 được áp dụng, trong khi C2 phụ thuộc vào C1. Do đó, để tạo ra kết quả trạng thái ổn định cuối cùng, bit nhớ phải lan truyền qua tất cả các trạng thái. Điều này làm tăng độ trễ lan truyền nhớ của mạch.

Độ trễ lan truyền của bộ cộng được tính bằng "độ trễ lan truyền của mỗi cổng nhân với số tầng trong mạch". Để tính toán một số lượng lớn bit, cần phải thêm nhiều tầng hơn, khiến độ trễ trở nên tệ hơn nhiều. Do đó, để giải quyết tình huống này, bộ cộng Carry Look-ahead đã ra đời.

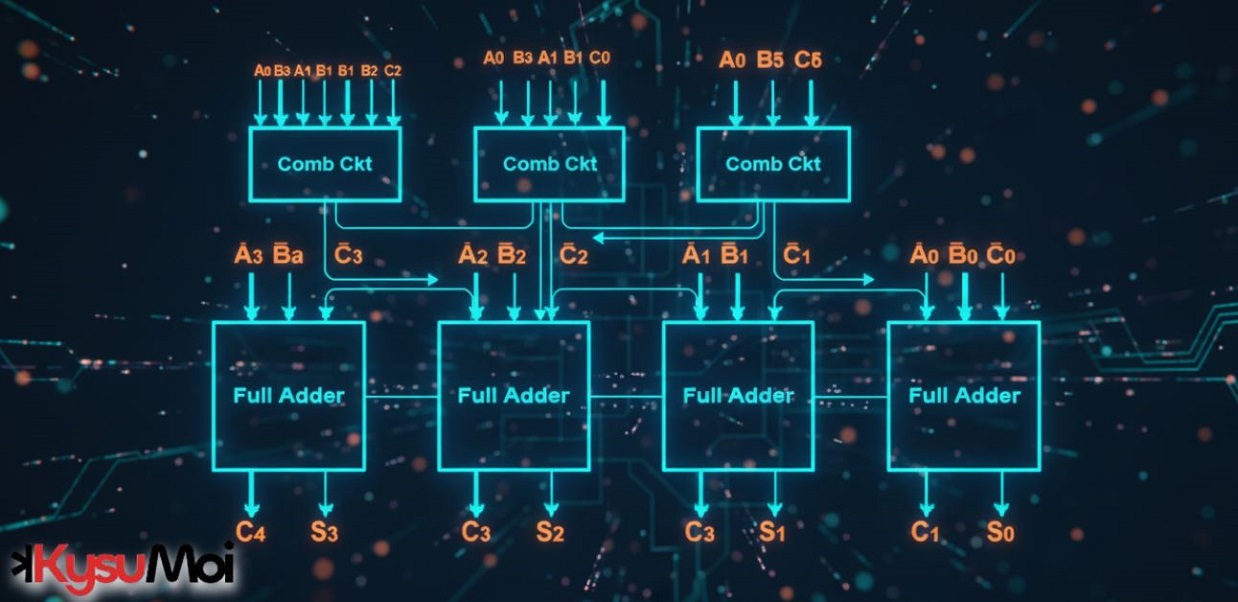

Để hiểu cách thức hoạt động của Bộ cộng nhìn trước mang, Bộ cộng nhìn trước mang 4 bit được mô tả bên dưới.

Trong bộ cộng này, đầu vào nhớ ở bất kỳ giai đoạn nào của bộ cộng đều độc lập với các bit nhớ được tạo ra ở các giai đoạn độc lập đó. Ở đây, đầu ra của bất kỳ giai đoạn nào chỉ phụ thuộc vào các bit được thêm vào ở các giai đoạn trước đó và đầu vào nhớ được cung cấp ở giai đoạn đầu. Do đó, mạch ở bất kỳ giai đoạn nào không phải chờ bit nhớ được tạo ra từ giai đoạn trước và bit nhớ có thể được đánh giá tại bất kỳ thời điểm nào.

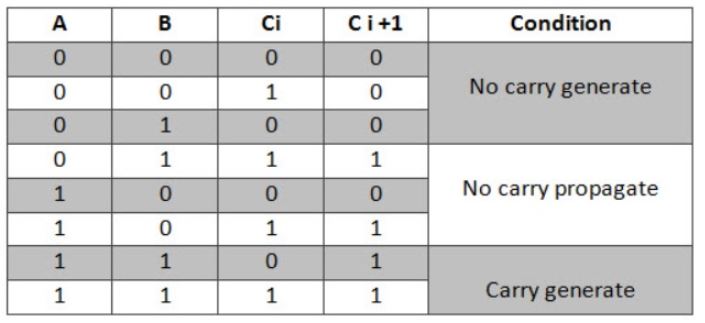

Bảng chân lý của bộ cộng nhìn trước mang

Để suy ra bảng chân lý của bộ cộng này, hai thuật ngữ mới được giới thiệu – Carry generate và Carry props. Carry generate Gi = 1 bất cứ khi nào có carry Ci+1 được tạo ra. Nó phụ thuộc vào đầu vào Ai và Bi. Gi bằng 1 khi cả Ai và Bi đều bằng 1. Do đó, Gi được tính như sau: Gi = Ai. Bi.

Pi lan truyền mang theo liên quan đến sự lan truyền mang theo từ Ci đến Ci+1. Nó được tính như sau: Pi = Ai ⊕ Bi. Bảng chân lý của bộ cộng này có thể được suy ra từ việc sửa đổi bảng chân lý của bộ cộng đầy đủ.

Sử dụng các số hạng Gi và Pi, Tổng Si và Carry Ci+1 được đưa ra như sau –

- Si = Pi ⊕ Gi.

- Ci+1 = Ci.Pi +Gi.

Do đó, các bit mang C1, C2, C3 và C4 có thể được tính như sau

- C1 = C0.P0+G0.

- C2 = C1.P1+G1 = ( C0.P0+G0).P1+G1.

- C3 = C2.P2+G2 = (C1.P1+G1).P2+G2.

- C4 = C3.P3+G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Có thể thấy từ các phương trình rằng bit nhớ Ci+1 chỉ phụ thuộc vào bit nhớ C0 chứ không phụ thuộc vào các bit nhớ trung gian.

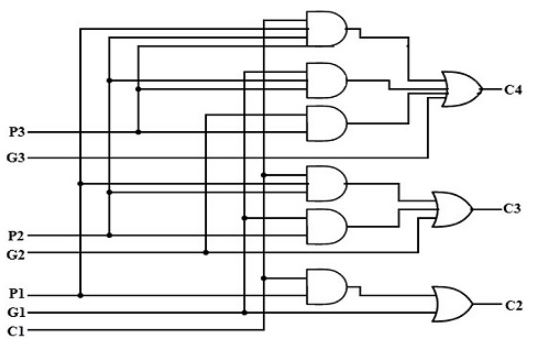

Sơ đồ mạch điện

Các phương trình trên được thực hiện bằng cách sử dụng mạch tổ hợp hai cấp cùng với cổng AND, OR, trong đó các cổng được cho là có nhiều đầu vào.

Mạch tạo đầu ra mang theo của bộ cộng nhìn trước mang theo

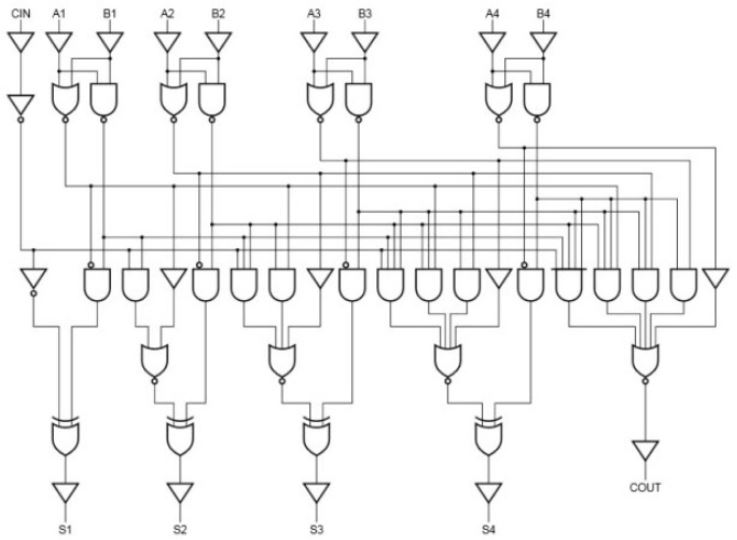

Mạch cộng nhìn trước Carry Look-head Adder cho 4 bit được đưa ra bên dưới.

Mạch cộng hướng trước 8 bit và 16 bit có thể được thiết kế bằng cách kết hợp mạch cộng 4 bit với logic nhớ.

Ưu điểm của Carry Look-ahead Adder

Trong bộ cộng này, độ trễ lan truyền được giảm thiểu. Ngõ ra nhớ ở bất kỳ giai đoạn nào chỉ phụ thuộc vào bit nhớ ban đầu của giai đoạn bắt đầu. Sử dụng bộ cộng này, có thể tính toán các kết quả trung gian. Bộ cộng này là bộ cộng nhanh nhất được sử dụng để tính toán.

Ứng dụng

Bộ cộng nhìn trước mang tốc độ cao được sử dụng như IC. Do đó, việc nhúng bộ cộng vào mạch rất dễ dàng. Bằng cách kết hợp hai hoặc nhiều bộ cộng, các phép tính của hàm boolean bit cao hơn có thể được thực hiện dễ dàng. Ở đây, việc tăng số lượng cổng cũng ở mức vừa phải khi sử dụng cho các bit cao hơn.

Bộ cộng này có sự đánh đổi giữa diện tích và tốc độ. Khi được sử dụng cho các phép tính bit cao hơn, nó cung cấp tốc độ cao nhưng độ phức tạp của mạch cũng tăng lên, do đó diện tích chiếm dụng của mạch cũng tăng theo. Bộ cộng này thường được triển khai dưới dạng các mô-đun 4 bit được ghép nối tiếp nhau khi được sử dụng cho các phép tính cao hơn. Bộ cộng này đắt hơn so với các bộ cộng khác.

Đối với tính toán boolean trong máy tính, bộ cộng đang được sử dụng thường xuyên. Charles Babbage đã triển khai một cơ chế dự đoán bit nhớ trong máy tính, nhằm giảm độ trễ do bộ cộng gợn sóng nhớ gây ra . Khi thiết kế một hệ thống, tốc độ tính toán là yếu tố quyết định hàng đầu đối với nhà thiết kế. Năm 1957, Gerald B. Rosenberger đã được cấp bằng sáng chế cho Bộ cộng Binary Carry Look-ahead hiện đại. Dựa trên phân tích độ trễ cổng và mô phỏng, các thí nghiệm đang được tiến hành để cải tiến mạch của bộ cộng này để làm cho nó thậm chí còn nhanh hơn.