Bộ tổng hợp tần số PLL kỹ thuật số

Bộ tổng hợp tần số PLL kỹ thuật số sử dụng các thành phần kỹ thuật số để tạo ra tín hiệu đầu ra ổn định ở tần số mong muốn.

Bộ tổng hợp RF kỹ thuật số PLL (PLL digital RF synthesizer) được đặt tên như vậy vì nó sử dụng các kỹ thuật số để điều khiển tần số đầu ra. Trong một số trường hợp, loại tổng hợp này còn được gọi là tổng hợp kỹ thuật số gián tiếp, vì tín hiệu đầu ra được tạo ra gián tiếp thông qua vòng khóa pha (PLL) thay vì trực tiếp bằng cách cộng, trừ, v.v.

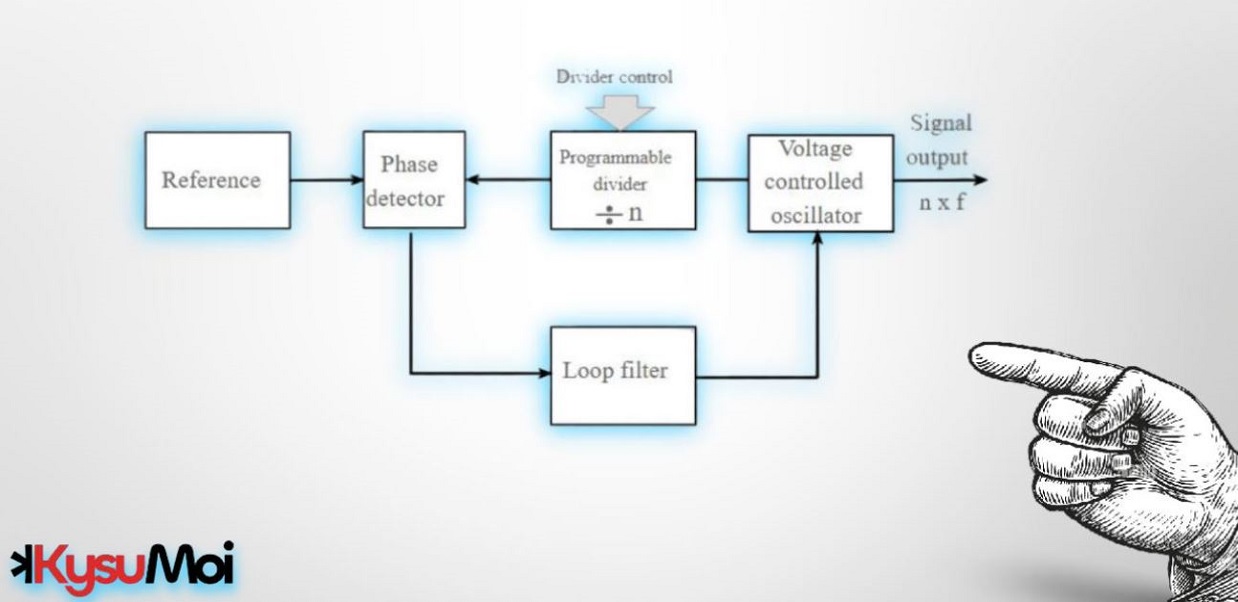

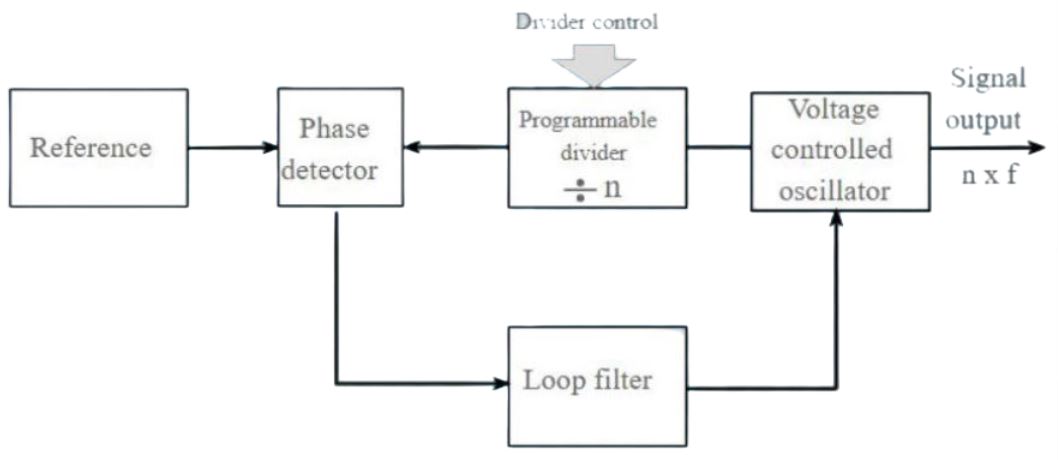

Bộ tổng hợp PLL kỹ thuật số sử dụng bộ chia kỹ thuật số nằm giữa VCO và bộ tách pha. Vì bộ chia sử dụng kỹ thuật số, nên có thể thay đổi tỷ lệ chia và thay đổi đầu ra từ bộ tổng hợp vòng khóa pha.

Bộ tổng hợp PLL kỹ thuật số đặc biệt hữu ích vì chúng có thể được điều khiển bằng một bộ chuỗi số, có thể được điều khiển bởi bộ vi xử lý hoặc bộ điều khiển. Điều này làm tăng đáng kể chức năng của các hệ thống sử dụng bộ tổng hợp PLL kỹ thuật số.

Hiện nay có nhiều chip tổng hợp RF có thông số kỹ thuật giúp thiết kế mạch RF trở nên đơn giản nhất có thể, giúp thiết kế RF dễ dàng và ứng dụng trở nên thú vị.

Cơ bản về bộ tổng hợp kỹ thuật số

Bộ tổng hợp tần số PLL kỹ thuật số sử dụng vòng khóa pha làm cơ sở.

Một vòng khóa pha bao gồm một số khối mạch: khối tham chiếu, bộ phát hiện pha, bộ dao động điều khiển bằng điện áp và bộ lọc. Về cơ bản, vòng lặp so sánh pha của tín hiệu từ mạch tham chiếu và VCO, sau đó đưa tín hiệu đầu ra của bộ phát hiện pha trở lại cực điều khiển của VCO thông qua bộ lọc.

Đầu ra của bộ phát hiện pha cảm nhận tần số VCO hướng về tần số tham chiếu, cuối cùng đạt đến điểm mà điện áp không đổi được đặt vào các cực điều khiển VCO, nghĩa là có độ lệch pha không đổi giữa tín hiệu tham chiếu và tín hiệu VCO. Vì độ lệch pha không thay đổi, điều này có nghĩa là tần số VCO và tín hiệu tham chiếu hoàn toàn giống nhau, và vòng lặp được khóa.

Ghi chú về Vòng khóa pha (PLL):

Vòng khóa pha (PLL) là một bộ tạo sóng vô tuyến (RF) rất hữu ích. PLL sử dụng khái niệm giảm độ lệch pha giữa hai tín hiệu, một tín hiệu tham chiếu và một bộ dao động cục bộ, để mô phỏng tần số của tín hiệu tham chiếu. Việc sử dụng khái niệm này cho phép PLL được sử dụng rộng rãi trong nhiều lĩnh vực, từ bộ tổng hợp tần số đến bộ giải điều chế FM và tái tạo tín hiệu.

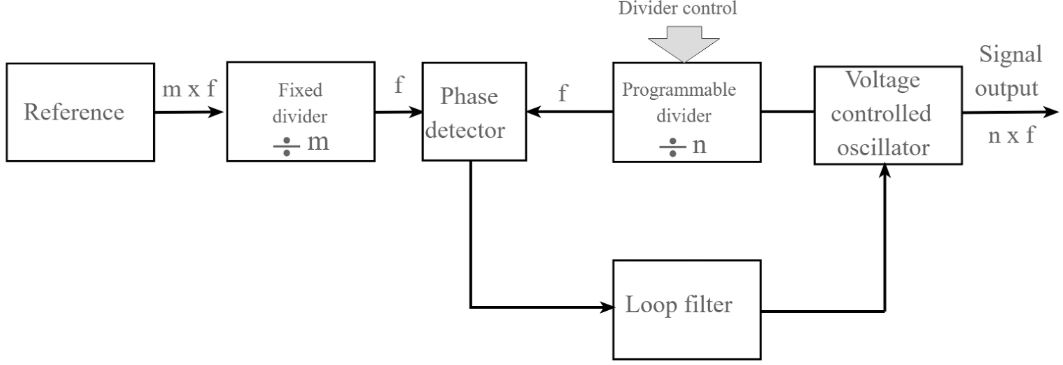

Để phát triển vòng khóa pha thành bộ tổng hợp tần số PLL kỹ thuật số, một bộ chia kỹ thuật số phải được đặt giữa VCO và bộ dò pha để chia tần số VCO xuống.

Cách thêm bộ chia kỹ thuật số vào vòng lặp tổng hợp tần số có thể được xem trong sơ đồ bên dưới.

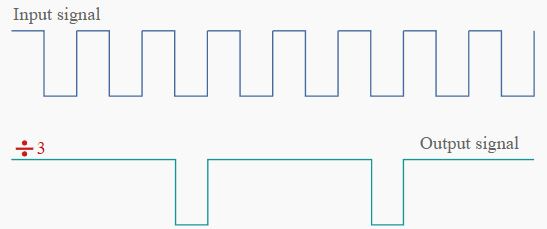

Bộ chia hoặc bộ đếm có thể lập trình được sử dụng trong nhiều lĩnh vực điện tử, bao gồm nhiều ứng dụng tần số vô tuyến. Bộ chia lấy một chuỗi xung, như minh họa bên dưới, và xuất ra tín hiệu chuỗi chậm hơn.

Trong mạch chia đôi, cứ hai xung đầu vào thì chỉ có một xung được đưa ra, v.v. Một số xung là hằng số, chỉ có một tỷ lệ chia. Các xung khác có thể lập trình được, và có thể sử dụng đầu vào kỹ thuật số hoặc logic để thiết lập tỷ lệ chia.

Khi thêm bộ chia vào mạch, mạch vòng khóa pha (PLL) vẫn cố gắng giảm thiểu độ lệch pha giữa hai tín hiệu đi vào bộ so sánh khi mạch ở trạng thái khóa. Hai tín hiệu đi vào bộ so sánh sẽ có cùng tần số. Để đạt được điều này, bộ dao động điều khiển bằng điện áp phải hoạt động ở tần số bằng tần số so sánh pha nhân với tỷ số chia.

Có thể thấy rằng nếu tỷ lệ phân chia thay đổi một, bộ dao động điều khiển bằng điện áp phải được thay đổi thành bội số tiếp theo của tần số tham chiếu, nghĩa là tần số bước của bộ tổng hợp sẽ bằng tần số đi vào bộ so sánh.

Tăng bước tần số

Từ hoạt động của một bộ tổng hợp tần số kỹ thuật số cơ bản, có thể thấy rằng tần số đầu ra bằng 'n' lần tần số so sánh pha, trong đó 'n' là tỷ số chia. Thay đổi tỷ số chia đi một là mức thay đổi tần số nhỏ nhất có thể đạt được.

Từ kết quả thực nghiệm, có thể thấy rằng mức thay đổi tần số tối thiểu có thể đạt được bằng tần số tham chiếu, tức là tần số của bộ tách sóng pha. Trong dạng cơ bản của bộ tổng hợp tần số kỹ thuật số, tần số này bằng tần số tham chiếu.

Hầu hết các bộ tổng hợp cần có khả năng điều chỉnh tần số theo từng bước rất nhỏ nếu muốn sử dụng được. Các bước 10 kHz, 12,5 kHz hoặc 25 kHz thường là cần thiết cho các đài phát thanh hoạt động trên các kênh khác nhau, và đối với các đài phát thanh yêu cầu điều chỉnh liên tục, các bước 100 Hz hoặc ít hơn có thể là cần thiết.

Để đạt được điều này, cần phải giảm tần số so sánh, thường được thực hiện bằng cách sử dụng bộ dao động tham chiếu ở tần số khoảng một megahertz, sau đó chia tín hiệu này xuống tần số mong muốn bằng bộ chia hằng số. Điều này sẽ tạo ra tần số so sánh thấp.

Thông thường, bộ dao động tham chiếu hoạt động ở tần số vài MHz, thường là 5 MHz hoặc 10 MHz, vì ở những tần số này, hiệu suất tốt hơn và tinh thể có thể được sản xuất theo kích thước yêu cầu.

Việc sử dụng bộ chia tần số sau bộ dao động tham chiếu cho phép so sánh các tần số pha thấp trong khi vẫn giữ cho bộ dao động tham chiếu hoạt động ở tần số thuận tiện, thường là khoảng 10 MHz.

Khi phát triển một bộ tổng hợp kỹ thuật số có tần số tham chiếu thấp, điều này có nghĩa là bộ chia có thể lập trình sẽ có tỷ lệ chia cao hơn nhiều vì nó cần chia từ tần số đầu ra xuống tần số tham chiếu thấp hơn, điều này có thể dẫn đến các vấn đề về độ trễ thông qua bộ chia, cũng như nhiễu pha cao và các vấn đề khác.

Độ chính xác và độ ổn định của tần số PLL kỹ thuật số

Một vấn đề với các bộ dao động như bộ dao động chạy tự do là chúng không ổn định và khó hiệu chuẩn. Vì là mạch tương tự, chúng dễ bị trôi và có thể cần thêm bộ hiệu chuẩn để đảm bảo tần số chính xác. Trên thực tế, các radio cũ sử dụng bộ dao động chạy tự do điều chỉnh LC trong thiết kế RF thường tích hợp bộ hiệu chuẩn tinh thể để xác minh sự đồng bộ tần số.

May mắn thay, với bộ tổng hợp PLL kỹ thuật số, tần số được xác định bởi bộ dao động tinh thể, có nghĩa là hiệu suất của bộ dao động tinh thể quyết định độ ổn định tần số của toàn bộ bộ tổng hợp.

Trên thực tế, độ ổn định tần số xét về độ trôi tần số tính theo phần triệu được xác định bởi kết quả đầu ra cuối cùng.

Rõ ràng, độ ổn định tần số tuyệt đối về độ trôi (Hertz/°C) được nhân với tỷ số nhân tổng của vòng lặp. Nói cách khác, nếu bộ dao động tham chiếu chạy ở tần số 10 MHz và đầu ra cuối cùng ở 150 MHz, thì bất kỳ giá trị tuyệt đối nào của độ trôi đều được nhân với 150/10 = 15. Tuy nhiên, xét về độ trôi (phần triệu), giá trị này sẽ không đổi, vì đây là một tỷ lệ.

Ví dụ về bộ tổng hợp tần số PLL kỹ thuật số

Việc cung cấp các con số thực tế thường rất hữu ích trong việc hiểu cách thiết kế mạch RF hoặc các kỹ thuật khác hoạt động.

Ví dụ, một bộ dao động tham chiếu có thể hoạt động ở tần số 1 MHz. Để đạt được độ ổn định và hiệu suất tổng thể tốt nhất, cần có bộ dao động tinh thể, vì bộ dao động tinh thể hoạt động trong dải tần này mang lại hiệu suất tham chiếu tốt nhất. Tần số 1 MHz, 5 MHz và 10 MHz là các tần số phổ biến cho bộ dao động tham chiếu.

Đối với bộ tổng hợp 12,5 kHz, được sử dụng rộng rãi cho các đài phát thanh di động FM băng hẹp hoặc các trạm gốc truyền thông vô tuyến, để đạt được tần số hiệu chỉnh pha là 12,5 kHz, thiết kế mạch RF yêu cầu một bộ chia kỹ thuật số có tỷ lệ chia cố định là 80 (1 MHz chia cho 80 = 12,5 kHz).

Nếu đầu ra của bộ tổng hợp hoạt động trong khoảng từ 144 đến 146 MHz, bộ chia có thể lập trình phải có khả năng cung cấp tỷ lệ chia từ 11520 đến 11680.

Đây chỉ là một ví dụ, và có thể sử dụng các con số phù hợp để xác định dải tần số và kích thước bước mong muốn. Yêu cầu chính là không làm cho tỷ lệ phân chia tín hiệu quá lớn đến mức gây ra vấn đề về độ ổn định của vòng lặp hoặc nhiễu pha.

Bộ tổng hợp PLL kỹ thuật số và nhiễu pha

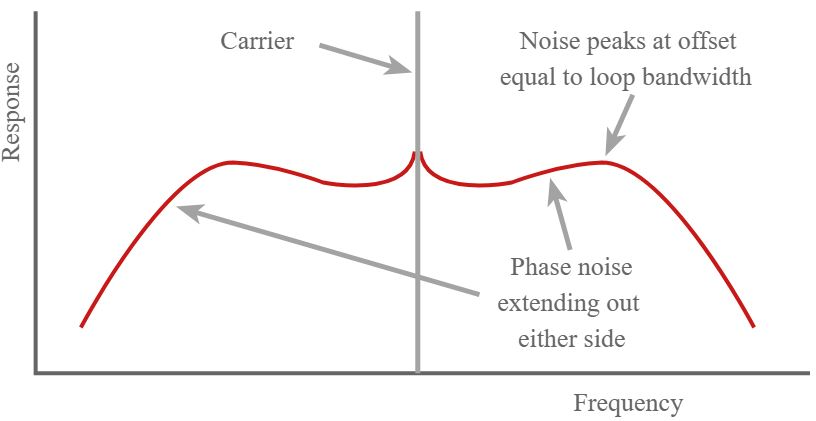

Một vấn đề với bộ tổng hợp PLL kỹ thuật số mạch đơn là nhiễu pha có thể dễ dàng trở thành vấn đề.

Nhiều máy thu phát VHF/UHF đời đầu bị nhiễu pha, dẫn đến hiệu suất thu kém và truyền mức nhiễu pha cao ở cả hai phía của sóng mang.

Điều quan trọng là phải giải quyết mọi vấn đề liên quan đến nhiễu pha như một phần của thiết kế mạch RF ban đầu cho bộ tổng hợp.

May mắn thay, mạch có thể được thiết kế để giảm mức độ nhiễu pha, mặc dù chỉ sử dụng một vòng lặp không hiệu quả lắm.

Bộ tổng hợp PLL kỹ thuật số là một trong những bộ tổng hợp tần số phổ biến nhất. Công nghệ này đã được chấp nhận rộng rãi và có sẵn nhiều loại IC tổng hợp, giúp việc thiết kế mạch RF trở nên dễ dàng. Bộ tổng hợp PLL kỹ thuật số cũng được sử dụng trong nhiều IC quy mô lớn được thiết kế cho các ứng dụng cụ thể, chẳng hạn như Bluetooth, Wi-Fi và nhiều ứng dụng khác.

Nhìn chung, bộ tổng hợp kỹ thuật số PLL đã trở nên phổ biến trong thiết kế mạch RF và là một thành phần thiết kế mạch điện tử rất phổ biến.