Giảm thiểu sự di cư điện tử trong thiết kế chip

Bài viết này thảo luận về các kỹ thuật và chiến lược để ngăn chặn hiện tượng di chuyển điện tử, một vấn đề quan trọng về độ tin cậy trong thiết kế chip.

Từ điện thoại thông minh đến máy tính xách tay, chúng ta sử dụng rất nhiều thiết bị hàng ngày dựa vào mạch tích hợp (IC) , hay chip, để hoạt động. Những con chip này được tạo thành từ hàng ngàn bóng bán dẫn và các kết nối, giúp truyền tín hiệu điện từ bộ phận này sang bộ phận khác của chip. Tuy nhiên, do nhu cầu về tốc độ và độ phức tạp đòi hỏi ngày càng nhiều năng lượng chạy qua các thiết bị ngày càng nhỏ hơn, dòng điện tập trung này có thể đe dọa hiệu suất chip, gây ra hiện tượng gọi là điện di.

Di cư điện tử là gì?

Sự di chuyển điện tử là sự chuyển động của các nguyên tử do dòng điện gây ra.

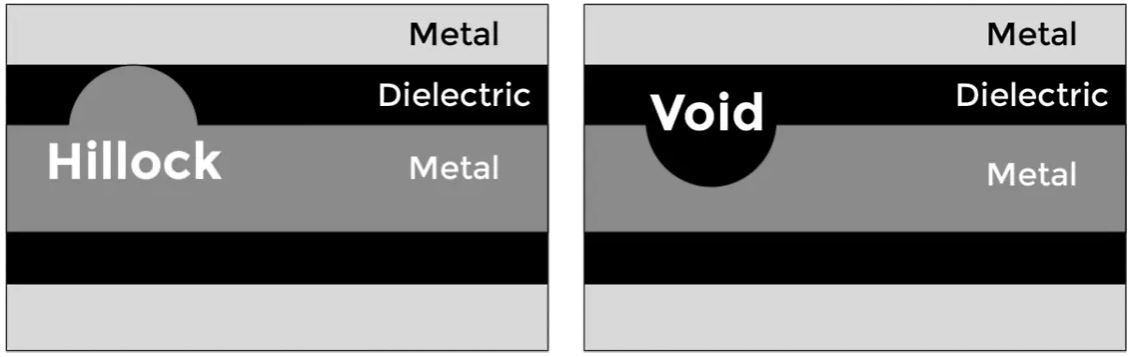

Chuyển động này có thể làm thay đổi cấu trúc vật lý của dây dẫn bằng cách tạo ra các lỗ rỗng hoặc gò đất, có thể gây ra đoản mạch, hở mạch, giảm hiệu suất hoặc hỏng thiết bị. Khi mật độ dòng điện tăng qua các liên kết, tốc độ di chuyển điện cũng tăng theo, khiến quá trình di chuyển điện trở nên mất kiểm soát. Trên thực tế, di chuyển điện là nguyên nhân chính gây ra hỏng hóc trong mạch điện.

Hình ảnh của một khoảng trống và một gò đất hình thành trong kết nối bán dẫn thông qua sự di chuyển điện tử của các nguyên tử kim loại ra khỏi một số khu vực và hướng tới những khu vực khác

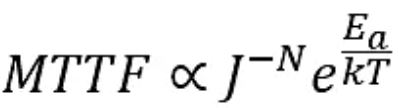

Tốc độ di chuyển điện tử có thể được tăng tốc bởi dòng điện cao hơn, nhiệt độ cao hơn, ứng suất cơ học tăng, khuyết tật trong dây dẫn và sự hiện diện của tạp chất. Những yếu tố này được thể hiện trong phương trình Black — một phương trình Arrhenius thực nghiệm mô tả hiện tượng này theo thời gian trung bình đến khi hỏng (MTTF):

- J: mật độ dòng điện

- N: hệ số tỷ lệ

- k: Hằng số Boltzmann

- T: nhiệt độ (tính bằng K)

- Ea: năng lượng hoạt hóa (tính bằng J)

Được phát triển bởi Robert Black vào năm 1969, phương trình của Black giúp các kỹ sư hiểu được tuổi thọ tiềm năng của một mạch điện bằng cách tính toán cách thức dòng điện di chuyển có thể ảnh hưởng đến thiết kế của họ. Phương trình này liên hệ MTTF với mật độ dòng điện, nhiệt độ và đặc tính vật liệu của dây dẫn.

Mật độ dòng điện: Vì dây lớn hơn có diện tích mặt cắt ngang lớn hơn nên chúng có mật độ dòng điện thấp hơn và ít bị ảnh hưởng bởi hiện tượng di chuyển điện tử hơn.

Nhiệt độ: Khi nhiệt độ tăng, các nguyên tử di chuyển nhanh hơn, làm tăng khả năng di cư điện tử.

Tính chất vật liệu: Một số vật liệu có khả năng chống lại sự di chuyển điện tử tốt hơn. Ví dụ, độ dẫn điện cao của đồng khiến nó trở thành lựa chọn phổ biến hơn nhôm.

Với việc các thiết bị điện tử ngày càng được thu nhỏ, khả năng xảy ra hiện tượng di chuyển điện tử — và các vấn đề mà nó gây ra — tăng lên đáng kể. Vì chip chịu trách nhiệm cho hiệu suất đáng tin cậy của các thiết bị này, hiện tượng di chuyển điện tử phải được giảm thiểu để duy trì chức năng của sản phẩm.

Làm thế nào để giảm thiểu tác động của sự di cư điện tử trong thiết kế chip

Để tránh sự khó chịu và nguy hiểm do kim loại di chuyển trong các linh kiện điện tử, các nhà thiết kế chip có thể sử dụng một số kỹ thuật, bao gồm:

- Tăng chiều rộng kết nối để giảm mật độ dòng điện.

- Sử dụng vật liệu có khả năng chống di chuyển điện tử cao như vàng và đồng.

- Chuyển hướng cường độ dòng điện bằng cách sử dụng các lỗ thông dự phòng.

- Giảm khoảng cách giữa các kết nối.

- Thiết kế mạch cho mức điện áp thấp hơn.

Tất nhiên, việc giải quyết hiện tượng di chuyển điện tử trong thiết kế chip có thể đòi hỏi sự kết hợp của nhiều kỹ thuật. Khi thiết kế các kết nối cho tích hợp quy mô rất lớn (VLSI), phần mềm mô phỏng có thể giúp bạn xác định các lựa chọn tốt nhất cho các yêu cầu dòng điện cụ thể của mình. Các nhà thiết kế chip phải phân tích mật độ dòng điện qua các kết nối và các lý do khác nhau dẫn đến điện trở tăng để dự đoán hiện tượng di chuyển điện tử trong chip.

Chiều dài kết nối tăng lên cùng với chiều rộng giảm, mật độ dòng điện cao và tản nhiệt kém đòi hỏi các quy tắc điện từ phức tạp hơn nhiều để giải quyết những thách thức này tại các nút công nghệ tiên tiến.

Kiểm tra và giám sát sự di chuyển điện tử trong thiết kế chip

Để đạt được độ tin cậy trong thiết kế chip, các kỹ sư phải cân nhắc sự đánh đổi giữa nhiều lựa chọn thiết kế khác nhau. Ví dụ, việc tăng chiều rộng kết nối sẽ làm giảm điện trở và mật độ dòng điện, đồng thời tăng điện dung. Hoặc, việc giảm khoảng cách giữa các kết nối sẽ hỗ trợ tích hợp, nhưng cũng sẽ làm tăng nhiễu xuyên âm.

Phần mềm mô phỏng như RedHawk-SC cho phép các nhà thiết kế chip dự đoán và phân tích hành vi của các kết nối để họ có thể quyết định cách phân phối năng lượng trong hệ thống trước khi chip được đưa vào sản xuất. Việc sử dụng mô phỏng để kiểm tra, xác thực và giám sát thiết kế chip không chỉ cải thiện hiệu suất điện tử mà còn giúp các công ty tránh được các lỗi tốn kém và việc thu hồi sản phẩm.

Kết luận

Di chuyển điện tử là một vấn đề quan trọng trong thiết kế và sản xuất chip. Mặc dù tác động của di chuyển điện tử có thể rất nghiêm trọng, nhưng có một số biện pháp có thể được thực hiện để ngăn ngừa hoặc giảm thiểu tác động của nó. Rủi ro di chuyển điện tử có thể được giảm thiểu bằng cách tối ưu hóa thiết kế các kết nối, lựa chọn vật liệu phù hợp, kiểm soát nhiệt độ và quản lý quy trình sản xuất một cách cẩn thận.

Với sự tiến bộ không ngừng của ngành điện tử, việc hiểu và giải quyết những thách thức do quá trình di chuyển điện tử đặt ra là điều cần thiết để đảm bảo độ tin cậy và tuổi thọ của chip.