Kiểm soát độ bất ổn nhiệt độ thiên vị âm (NBTI) để cải thiện độ tin cậy của thiết bị

Tìm hiểu cách chúng tôi chế ngự cơ chế suy thoái này để công nghệ của chúng ta có thể tồn tại lâu hơn.

Sự bất ổn định nhiệt độ do độ lệch âm là một vấn đề ngày càng nghiêm trọng tại các nút quy trình tiên tiến nhất, nhưng nó cũng tỏ ra cực kỳ khó kiểm soát bằng các phương pháp thông thường. Cuối cùng, điều đó có thể đang bắt đầu thay đổi.

NBTI là một cơ chế lão hóa trong transistor hiệu ứng trường, dẫn đến sự thay đổi đường cong đặc tính của transistor trong quá trình hoạt động. Kết quả có thể là mạch transistor hoạt động sai lệch theo hướng không mong muốn.

Cụ thể hơn, NBTI có thể làm tăng thời gian trễ cổng trong các ứng dụng kỹ thuật số, từ đó có thể dẫn đến vi phạm thời gian, làm sai lệch kết quả tính toán. Trong mạch tương tự, ngay cả những thay đổi nhỏ về đặc tính của FET cũng có thể ảnh hưởng tiêu cực đến độ chính xác của mạch. Ví dụ, các FET ghép cặp có thể lão hóa khác nhau và dẫn đến sai số trong bộ chuyển đổi tương tự sang số, Kay-Uwe Giering, cộng tác viên nghiên cứu tại Fraunhofer EAS , giải thích .

“Một vấn đề phức tạp nữa là các FET nhỏ của các nút công nghệ tiên tiến phải đối mặt với vấn đề biến thiên NBTI, trong khi số lượng khuyết tật liên quan đến NBTI giảm dần theo diện tích oxit cổng,” Giering nói. “Các đặc tính khuyết tật vẫn phân bố rộng rãi, do đó các FET có cùng hình dạng có thể lão hóa rất khác nhau. Do đó, sự suy giảm NBTI chịu ảnh hưởng của biến thiên thống kê, vốn đã được tính trung bình ở các bóng bán dẫn lớn hơn .”

Jim Dodrill, giám đốc kỹ thuật cấp cao của Nhóm Thiết kế Vật lý tại Arm, lưu ý rằng tốc độ trôi điện áp ngưỡng (Vt) từ NBTI tăng tốc ở điện áp cao - điều này có thể cần thiết cho nhiều thiết kế để đạt được mục tiêu hiệu suất - và ở nhiệt độ cao hơn, được thúc đẩy bởi hoạt động chuyển mạch tần số cao và các hiệu ứng nhiệt cục bộ . "Các hiệu ứng thời gian rõ rệt nhất khi điện áp thiết bị được giảm xuống để hoạt động ở mức công suất thấp."

Magdy Abadir, phó chủ tịch tiếp thị tại Helic , đồng tình. “Khi thiết bị cũ đi, NBTI làm tăng điện áp ngưỡng trong các thiết bị PMOS. Điều này dẫn đến tăng độ trễ và lỗi thời gian. Tác động của NBTI cao hơn ở các nút tiên tiến. Ngoài ra, tác động của NBTI tăng lên khi VDD giảm, đây là xu hướng phổ biến ở các nút tiên tiến nhằm giảm công suất.”

Hiểu về NBTI

Sự mất ổn định nhiệt độ phân cực âm là một cơ chế suy giảm ảnh hưởng đến transistor PMOS. Nó bắt nguồn từ những thay đổi tại giao diện giữa oxit cổng và kênh dẫn. Kết quả có thể là bất cứ điều gì, từ việc tăng điện áp ngưỡng và dòng rò đến giảm độ linh động, dòng thoát và độ dẫn điện.

“NBTI đã trở nên quan trọng hơn do quy mô quy trình được mở rộng”, Art Schaldenbrand, giám đốc sản phẩm cấp cao tại Cadence , cho biết . “Quy mô quy trình dẫn đến sự gia tăng điện trường trên các oxit cổng. Các thiết bị hoạt động ở nhiệt độ cao hơn do công suất tiêu tán lớn hơn và các lớp oxit cổng phức tạp hơn. Và tất cả những yếu tố này góp phần làm tăng khả năng bị ảnh hưởng bởi NBTI. Khi quy mô tiếp tục giảm, các bóng bán dẫn kênh n cũng bắt đầu cho thấy khả năng bị ảnh hưởng bởi sự bất ổn định nhiệt độ phân cực dương (PBTI).”

Nhưng NBTI cũng khó dự đoán. Schaldenbrand cho biết: "Điều khiến việc phân tích vấn đề trở nên phức tạp hơn nữa là, tùy thuộc vào cách thiết bị được vận hành/chịu áp lực, thiết bị có thể phục hồi sau hiệu ứng BTI. Vì NBTI làm tăng điện áp ngưỡng và giảm độ linh động, nó ảnh hưởng đến thời gian, công suất động, mạch rò rỉ của các cell pin chuẩn kỹ thuật số."

Ghép nối điện từ (EM) chỉ làm vấn đề thêm phức tạp. Nó có thể dẫn đến độ trễ biến thiên rất lớn, tùy thuộc vào điều kiện chuyển mạch của một tập hợp lớn các tín hiệu ghép nối.

“Những biến thiên độ trễ này làm giảm đáng kể biên độ thời gian, do đó khả năng chịu đựng các tác động lão hóa NBTI kém hơn và lỗi có thể xảy ra sớm hơn”, Abadir của Helic cho biết. “Khác với ghép nối điện dung, ghép nối từ tính có phạm vi ảnh hưởng rất rộng và khó có thể được bảo vệ. Do đó, ghép nối từ tính có thể xảy ra nhiều biến thiên độ trễ hơn so với ghép nối điện dung. Những biến thiên do ghép nối từ tính này cũng ảnh hưởng đến độ dao động xung nhịp và độ lệch trường hợp xấu nhất, làm trầm trọng thêm tình trạng thiếu biên độ thời gian. Biên độ chịu đựng của NBTI sau đó bị giảm đáng kể do ghép nối điện từ.”

Ngoài ra, sự kết hợp từ tính và hiệu ứng tự cảm vốn có trong mạng lưới phân phối điện (PDN) dẫn đến sự sụt giảm PDN, làm giảm giá trị hiệu dụng của nguồn cung cấp cho cổng CMOS . Ông cho biết, khi nguồn cung giảm, hiệu ứng NBTI được biết là sẽ tăng lên.

Theo Giáo sư Yehea Ismail của Đại học Hoa Kỳ tại Cairo, sự kết hợp từ tính được biết là gây ra hiện tượng vượt ngưỡng hoặc thiếu ngưỡng trong tín hiệu, điều này có thể trở nên đáng kể trong trường hợp chuyển mạch tệ nhất khi tín hiệu chuyển mạch theo cùng một hướng tạo ra từ trường cộng.

Ismail cho biết: “Những hiện tượng vượt ngưỡng và thiếu ngưỡng này có thể dễ dàng làm trầm trọng thêm các hiệu ứng NBTI thông qua một số cơ chế. Hiện tượng vượt ngưỡng dẫn đến điện trường cao, có thể gây ra hiệu ứng electron nóng, làm thay đổi điện áp ngưỡng theo cách làm tăng đáng kể hiệu ứng NBTI. Ngoài ra, những dao động tín hiệu này xung quanh VDD tại đầu vào của một cổng dẫn đến giá trị hiệu dụng '1' khác với VDD và làm thay đổi hiệu ứng NBTI. Hơn nữa, hiện tượng vượt ngưỡng dẫn đến dòng điện hai chiều trong các transistor PMOS vượt quá dòng điện CMOS đơn hướng thông thường cần thiết để nạp điện dung đầu ra đến VDD, dẫn đến hiện tượng quá nhiệt trong các transistor PMOS và làm tăng NBTI.”

Cải thiện độ tin cậy

Theo đó, việc tăng độ tin cậy thiết kế có thể đạt được bằng nhiều cách, Ismail cho biết. “Đầu tiên, mô hình hóa đúng các đặc tính vật lý của thiết kế (ví dụ: trích xuất RLCK) và kết hợp các mô hình chính xác này vào việc tính toán các chỉ số hiệu suất chính của thiết kế (độ trễ, VDD hiệu dụng, mức tiêu thụ điện năng, nhiễu ghép nối, v.v.) thay vì sử dụng các mô hình đơn giản rồi dựa vào các biên độ tùy ý và tốn kém. Lưu ý rằng nếu có nhiều nguồn biến thiên không được mô hình hóa chính xác, việc sử dụng một số biên độ tùy ý sẽ không giải quyết được các vấn đề thiết kế chính và có thể cực kỳ tốn kém.”

Ngoài ra, độ tin cậy của thiết kế cũng có thể được tăng lên bằng cách sử dụng các mô hình lão hóa thích hợp để ước tính độ tuổi dự kiến của các thiết bị trong điều kiện sử dụng thực tế và môi trường, ông nói thêm.

Dodrill của Arm gợi ý rằng cách đơn giản nhất để tính đến sự lão hóa của bóng bán dẫn ở cấp độ SoC là bao gồm biên độ thời gian bổ sung cho thiết lập và giữ. "Một cách phức tạp hơn một chút để tính đến điều này là đặt phạm vi quan trọng thành ít nhất 10% chu kỳ xung nhịp để thiết lập và bao gồm biên độ thời gian bổ sung cho các đường dẫn giữ bao gồm xung nhịp có cổng . Việc mô tả đặc tính của IP để bao gồm các tác động của lão hóa, như NBTI, sẽ không hữu ích nếu không có giải pháp STA cấp độ đường dẫn. Giải pháp cuối cùng là phần mềm EDA tính đến lão hóa khi thực hiện phân tích thời gian tĩnh, đây không phải là một nhiệm vụ nhỏ; mỗi bóng bán dẫn có một bối cảnh chuyển mạch duy nhất. Việc mô hình hóa, phân tích và đặc tính bổ sung sẽ bổ sung vào thiết kế và xác thực IP và thiết kế vốn đã tốn nhiều CPU, nhưng điều này là bắt buộc nếu chúng ta muốn tính đến đúng các tác động của NBTI mà không thêm các biên độ quá bi quan."

Các mô hình NBTI tiên tiến, bao gồm cả biến thiên NBTI, đang được phát triển và cung cấp cho các nhà thiết kế mạch, theo Giering của Fraunhofer. Không giống như các mô hình NBTI thực nghiệm truyền thống, các mô hình tiên tiến khai thác các hiểu biết vật lý để cho phép dự đoán độ chính xác cao về quá trình lão hóa của NBTI.

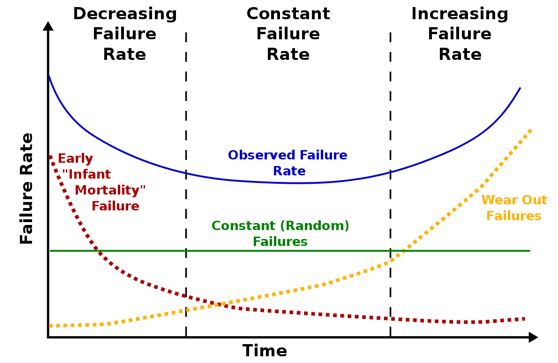

Ngay cả khi có một số công nghệ được sử dụng, Ahmed Ramadan, giám đốc kỹ thuật sản phẩm cấp cao của Chương trình AMS Foundry tại Mentor, một doanh nghiệp của Siemens , cho biết NBTI là một trong những mối đe dọa quan trọng nhất đối với các thiết bị MOSFET—dù là NMOS hay PMOS—trong các mạch VLSI hiện nay. “Khi ứng suất điện trên bóng bán dẫn tăng lên, sẽ có những vấn đề liên quan đến giao diện phía silicon. Với lượng ứng suất cao và nhiệt độ cao được áp dụng trên giao diện này, các bẫy sẽ được tạo ra bên trong lớp oxit, khiến thiết bị bị mài mòn dần dần. Đó là sự mài mòn dần dần. Nó không phải là sự mài mòn đột ngột có thể xảy ra trong quá trình thử nghiệm ban đầu của thiết bị và do đó. Đó là lý do tại sao nó nguy hiểm. Bạn không thể thoát ra khỏi nó ngay lập tức khi thiết bị đang chịu áp lực. ”

Mọi chuyện chỉ càng tệ hơn từ đó. "Cuối cùng, tất cả các mạch điện sẽ hỏng vì các bóng bán dẫn trở nên chậm hơn", Ramadan nói. "Cũng có những vấn đề liên quan đến sự không tương thích giữa hai thiết bị. Bạn có thể có một thiết bị bị suy giảm nhiều hơn thiết bị kia, có thể là một phần của một cặp vi sai, vì vậy chúng không còn tương thích nữa. Và một trong những vấn đề có thể xảy ra trong mạch điện là dòng rò có thể trở nên lớn hơn."

Việc dự đoán khả năng phục hồi sau NBTI cũng không hề đơn giản. "Để dự đoán khả năng phục hồi đó, cần phải có một mô hình động tốt có thể sử dụng trong mô phỏng và có thể tính đến hiệu ứng phục hồi này", ông nói. "Khi nói đến các nút công nghệ tiên tiến, bạn sẽ thấy các mạch tích hợp hoạt động lâu hơn trước đây, điều này có thể khiến nhiệt độ chip tăng theo thời gian."

Nhiệt độ cao hơn có ảnh hưởng đến NBTI. Các oxit cổng siêu mỏng cũng vậy.

Ramadan cho biết: “Rất nhiều thiết bị trong các nút công nghệ tiên tiến sử dụng oxit siêu mỏng cho các cổng, và các kỹ thuật để giảm thiểu việc sử dụng oxit siêu mỏng có thể gây rò rỉ. Để giải quyết vấn đề rò rỉ này, người ta sử dụng điện môi k cao kết hợp với cổng kim loại. Nếu sử dụng điện môi k cao, điều đó có nghĩa là bạn có thể đưa thêm nhiều bẫy giao diện silicon dioxide vào. Đổi lại, chúng có thể tạo ra khả năng suy thoái cao hơn do một nguyên nhân nào đó như NBTI. Đây là lý do tại sao vấn đề này lại càng nghiêm trọng hơn trong các nút công nghệ tiên tiến, nơi sử dụng oxit mỏng sử dụng điện môi k cao.”

Hướng tới nhiều tiêu chuẩn hơn

Việc mỗi nhà cung cấp công cụ EDA hiện nay đều sử dụng mô hình độc quyền của riêng mình để dự đoán khả năng phục hồi không có ích gì, nhưng tiến bộ cũng đang diễn ra ở đó.

“Hiện nay chưa có mô hình chuẩn nào được áp dụng,” Ramadan nói. “Các nhà cung cấp EDA đều đã phát triển các mô hình cho việc này. Tuy nhiên, trên toàn ngành, các xưởng đúc đang phát triển mô hình của họ, các tổ chức cũng đang phát triển mô hình của họ, vì vậy các ủy ban tiêu chuẩn hóa, bao gồm Liên minh Mô hình Nhỏ gọn (CMC), đang nỗ lực rất nhiều để phát triển một mô hình chuẩn cho quá trình lão hóa, không chỉ nhắm đến NBTI mà còn cả quá trình phun chất mang nóng, TDDB (phân hủy oxit cổng phụ thuộc thời gian) và bất kỳ cơ chế suy thoái nào khác. Đây là nỗ lực hợp tác giữa các công ty khác nhau, bao gồm các xưởng đúc, nhà cung cấp EDA, IDM và các viện giáo dục như Đại học California tại Berkeley, Đại học Hiroshima và các tổ chức khác.”

Một lần nữa, khi mô phỏng độ tin cậy và lão hóa ngày càng trở nên quan trọng với các nút tiên tiến, NBTI là một phần quan trọng của thiết kế và sản xuất cần được giải quyết.

Về phía xưởng đúc, một số nhà sản xuất bán dẫn có thể xử lý mọi thứ, từ cung cấp và điều chỉnh mô hình cho đến công nghệ của họ. Các mô hình này có thể là mô hình vật lý, hoặc một phần vật lý, và một phần thực nghiệm để phù hợp với công nghệ. Một số xưởng đúc thậm chí còn phát triển giao diện lão hóa riêng, có thể được sử dụng để chạy mô phỏng mạch trên tất cả các giải pháp của nhà cung cấp EDA hiện nay.

Giao diện lão hóa này là cần thiết để chạy mô phỏng lão hóa, và hiện nay mỗi nhà cung cấp công cụ EDA lớn nhất đều có giải pháp riêng cho lão hóa. Ngày càng có nhiều lo ngại rằng các xưởng đúc có thể không muốn tiếp tục hỗ trợ tất cả các giải pháp này, và do đó, CMC đã làm việc trong bảy năm qua để phát triển một giao diện lão hóa tiêu chuẩn, giao diện mô hình mở (OMI). Giao diện này không phụ thuộc vào trình mô phỏng, vì vậy nếu được hỗ trợ bởi bất kỳ công cụ EDA nào từ các nhà cung cấp EDA khác nhau, nó có thể cung cấp cho họ một giao diện duy nhất mà các xưởng đúc có thể sử dụng. Tất cả những gì họ cần làm là phát triển mô hình của riêng mình, đặt nó vào giao diện và nó sẽ hoạt động trên nhiều nhà cung cấp EDA khác nhau.

Những người ủng hộ cho rằng điều này cũng sẽ giải phóng khách hàng khỏi việc phụ thuộc vào một giải pháp duy nhất từ một nhà cung cấp EDA duy nhất. Thay vì tập trung vào giao diện, các nỗ lực của ngành có thể tập trung vào việc làm thế nào để các mô hình thể hiện chính xác công nghệ mà ngành và khách hàng hiện nay cần.

Cho đến khi thảo luận về tiêu chuẩn được giải quyết, nhiều bên sẽ tiếp tục nỗ lực cải thiện độ tin cậy của thiết bị bằng cách giải quyết vấn đề lão hóa và NBTI theo mọi cách có thể.