Kỹ thuật đồng hồ tiên tiến cho thiết kế tốc độ cao

Khám phá các kỹ thuật đo thời gian tiên tiến để đạt hiệu suất tốc độ cao tối ưu.

Việc theo đuổi hiệu suất cao hơn trong thiết kế FPGA đã đặt trọng tâm ngày càng cao vào việc quản lý xung nhịp. Trong thời đại kỹ thuật số, nơi tốc độ là tối quan trọng, việc thành thạo các kỹ thuật xung nhịp không còn là một điều xa xỉ mà là một điều cần thiết. Bài viết này đi sâu vào các chiến lược xung nhịp nâng cao, cung cấp hiểu biết toàn diện về cách tối ưu hóa tín hiệu xung nhịp để đạt hiệu suất FPGA tối đa. Chúng ta sẽ khám phá các kỹ thuật khác nhau, ý nghĩa của chúng và những cân nhắc thực tế để triển khai thành công.

Khi thiết kế FPGA ngày càng phức tạp và đòi hỏi tốc độ cao hơn, vai trò của xung nhịp càng trở nên quan trọng hơn. Quản lý xung nhịp hiệu quả có thể tạo nên sự khác biệt giữa một thiết kế chỉ đáp ứng được thông số kỹ thuật và một thiết kế vượt xa kỳ vọng về hiệu suất. Hướng dẫn này nhằm mục đích trang bị cho bạn kiến thức và công cụ cần thiết để giải quyết các thách thức xung nhịp nâng cao và đạt được kết quả vượt trội trong các dự án FPGA của bạn.

Hiểu về miền đồng hồ

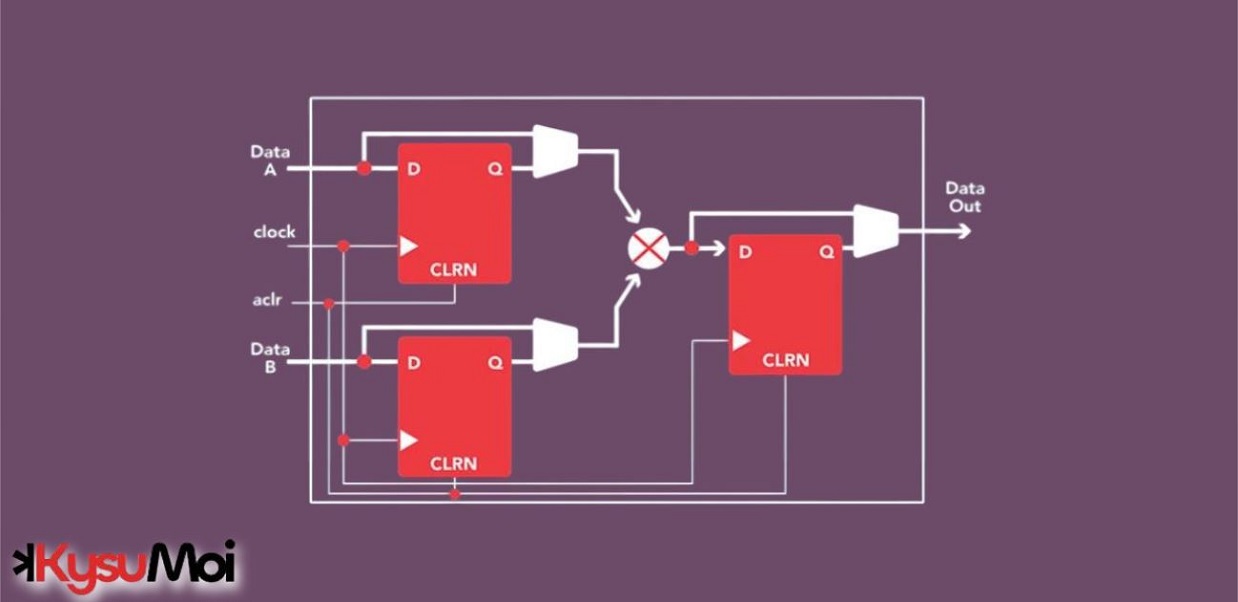

Trước khi đi sâu vào các kỹ thuật nâng cao, điều quan trọng là phải nắm vững các nguyên tắc cơ bản của miền xung nhịp. Miền xung nhịp là một vùng của mạch được đồng bộ hóa với một nguồn xung nhịp duy nhất. Nhiều miền xung nhịp cùng tồn tại trong hầu hết các FPGA, thường dẫn đến những thách thức trong việc truyền dữ liệu và đồng bộ hóa. Hiểu được hiện tượng giao thoa miền xung nhịp (CDC) và các mối nguy hiểm liên quan là điều cần thiết để ngăn ngừa trạng thái siêu ổn định và đảm bảo tính toàn vẹn dữ liệu.

Giao thoa miền đồng hồ (CDC)

CDC xảy ra khi tín hiệu được truyền giữa các miền xung nhịp khác nhau. Sự truyền tín hiệu này có thể dẫn đến tình trạng siêu ổn định, một tình trạng mà một flip-flop hoặc chốt chuyển sang trạng thái không xác định, có khả năng gây ra hành vi không thể đoán trước. Để giảm thiểu các vấn đề về CDC, các nhà thiết kế phải triển khai các kỹ thuật đồng bộ hóa như:

- Bộ đồng bộ hai flip-flop : Một phương pháp đơn giản nhưng hiệu quả trong đó tín hiệu được truyền qua hai flip-flop trong miền xung nhịp đích, giúp giảm khả năng xảy ra hiện tượng siêu ổn định.

- FIFO không đồng bộ : Được sử dụng để lưu trữ dữ liệu giữa các miền xung nhịp khác nhau, cho phép truyền dữ liệu an toàn và đáng tin cậy.

- Giao thức bắt tay : Việc triển khai cơ chế bắt tay đảm bảo dữ liệu được truyền và xác nhận an toàn giữa các miền đồng hồ.

Tầm quan trọng của miền đồng hồ

Miền xung nhịp là một phần không thể thiếu trong thiết kế FPGA, đặc biệt là trong các hệ thống có yêu cầu xung nhịp khác nhau. Các khối khác nhau trong FPGA có thể hoạt động ở các tần số khác nhau, đòi hỏi việc quản lý miền xung nhịp cẩn thận để đảm bảo tính ổn định và hiệu suất tổng thể của hệ thống. Việc xử lý miền xung nhịp đúng cách không chỉ cải thiện hiệu suất mà còn nâng cao tính bền vững và độ tin cậy của thiết kế.

Kỹ thuật chấm công nâng cao

Để đạt được thiết kế FPGA tốc độ cao, cần áp dụng các kỹ thuật tạo xung nhịp tiên tiến. Các kỹ thuật này tập trung vào việc tối ưu hóa mạng lưới phân phối xung nhịp, tạo ra tín hiệu xung nhịp chính xác, giảm mức tiêu thụ điện năng và đảm bảo hoạt động đáng tin cậy trong nhiều điều kiện khác nhau.

1. Tối ưu hóa mạng phân phối xung nhịp (CDN)

Một CDN được thiết kế tốt chính là xương sống của bất kỳ FPGA tốc độ cao nào. Dưới đây là những cân nhắc chính:

Quản lý độ lệch đồng hồ

Việc giảm thiểu độ lệch xung nhịp, tức là sự khác biệt về thời gian đến của tín hiệu xung nhịp tại các điểm khác nhau trong mạch, là rất quan trọng. Các kỹ thuật để quản lý độ lệch xung nhịp bao gồm:

- Chèn bộ đệm : Đặt bộ đệm một cách chiến lược dọc theo đường dẫn xung nhịp để cân bằng độ trễ và đảm bảo tín hiệu xung nhịp đến đồng bộ.

- Bù độ trễ : Sử dụng các phần tử trễ để cân bằng độ trễ đường dẫn, đảm bảo rằng tất cả các phần của mạch đều nhận được tín hiệu xung nhịp cùng một lúc.

- Định tuyến cẩn thận : Thiết kế đường dẫn xung nhịp để giảm thiểu sự khác biệt về độ dài định tuyến, do đó làm giảm độ lệch.

Giảm rung động

Độ trễ (jitter) là sự thay đổi về thời gian tín hiệu xung nhịp, có thể ảnh hưởng xấu đến hiệu suất của các mạch tốc độ cao. Để giảm thiểu độ trễ:

- Nguồn xung nhịp có độ nhiễu thấp : Sử dụng bộ dao động hoặc đồng hồ tinh thể chất lượng cao, độ nhiễu thấp làm nguồn xung nhịp chính.

- Tổng hợp cây đồng hồ thích hợp : Thiết kế cây đồng hồ để giảm thiểu sự tích tụ độ nhiễu qua mạng.

Tính toàn vẹn của quyền lực

Việc đảm bảo cung cấp đủ điện cho CDN là rất quan trọng để duy trì tính toàn vẹn của tín hiệu. Sụt áp và nhiễu nguồn có thể làm suy giảm tín hiệu xung nhịp. Các kỹ thuật để duy trì tính toàn vẹn của nguồn bao gồm:

- Tụ điện tách rời : Đặt tụ điện gần bộ đệm xung nhịp để ổn định nguồn điện.

- Mạng lưới phân phối điện : Thiết kế mạng lưới phân phối điện mạnh mẽ để cung cấp mức điện áp ổn định cho các thành phần xung nhịp.

Chấm dứt

Sử dụng các kỹ thuật kết thúc phù hợp giúp cân bằng trở kháng đặc trưng của các đường tín hiệu xung nhịp, giảm phản xạ tín hiệu và đảm bảo tín hiệu xung nhịp sạch. Các phương pháp kết thúc bao gồm:

- Kết thúc chuỗi : Đặt một điện trở nối tiếp với đường xung nhịp để phù hợp với trở kháng và hấp thụ phản xạ.

- Kết thúc song song : Sử dụng điện trở để nối đất hoặc cung cấp điện áp ở cuối đường xung nhịp để phù hợp với trở kháng.

2. Vòng khóa pha (PLL) để tạo xung nhịp

PLL là thành phần linh hoạt để tạo ra nhiều tần số và pha xung nhịp từ một xung nhịp tham chiếu duy nhất. Việc sử dụng PLL hiệu quả là rất quan trọng:

Vị trí PLL

Đặt PLL một cách chiến lược trong FPGA để giảm thiểu nhiễu và hiệu ứng ghép nối. PLL nên được đặt cách xa các mạch số và vùng cung cấp điện nhiễu để đảm bảo hoạt động ổn định.

Thiết kế bộ lọc vòng lặp

Việc tối ưu hóa các tham số bộ lọc vòng cho PLL là rất cần thiết để duy trì tính ổn định và đạt được đáp ứng tức thời tốt. Bộ lọc vòng ảnh hưởng đến băng thông và hệ số giảm chấn của PLL, từ đó ảnh hưởng đến khả năng khóa xung nhịp tham chiếu của nó.

Bộ đệm đầu ra

Việc sử dụng bộ đệm đầu ra thích hợp để điều khiển tải xung nhịp đảm bảo rằng các tín hiệu xung nhịp do PLL tạo ra duy trì tính toàn vẹn và đáp ứng các yêu cầu về thời gian của mạch được kết nối.

Hiệu suất Jitter

Xem xét thông số kỹ thuật về độ nhiễu PLL và tác động của chúng lên toàn bộ hệ thống. PLL có độ nhiễu thấp góp phần cải thiện hiệu suất hệ thống bằng cách cung cấp tín hiệu xung nhịp sạch và ổn định.

3. Cổng đồng hồ

Cổng đồng hồ có thể giảm mức tiêu thụ điện năng bằng cách bật và tắt tín hiệu đồng hồ một cách linh hoạt. Tuy nhiên, nó cũng gây ra những thách thức về thiết kế:

Lựa chọn tế bào cổng

Lựa chọn các cell gating phù hợp dựa trên hiệu suất và yêu cầu về công suất. Các cell gating khác nhau mang lại nhiều sự cân bằng giữa khả năng tiết kiệm điện năng và độ phức tạp khi triển khai.

Xử lý siêu ổn định

Triển khai logic đồng bộ hóa phù hợp để ngăn chặn trạng thái siêu ổn định khi bật hoặc tắt đồng hồ. Điều này đảm bảo đồng hồ có cổng không gây ra rủi ro về thời gian.

Tối ưu hóa năng lượng

Cân bằng giữa tiết kiệm điện năng và tác động đến hiệu suất. Cơ chế kiểm soát xung nhịp có thể giảm đáng kể mức tiêu thụ điện năng ở các mô-đun nhàn rỗi hoặc hoạt động thấp, nhưng phải được thiết kế cẩn thận để tránh làm giảm hiệu suất hệ thống.

4. Tổng hợp cây đồng hồ (CTS)

CTS là một bước quan trọng trong thiết kế FPGA, nhằm giảm thiểu độ lệch và độ trễ xung nhịp. Các kỹ thuật CTS tiên tiến bao gồm:

Chèn bộ đệm

Chèn bộ đệm một cách chiến lược dọc theo đường dẫn xung nhịp để cân bằng độ trễ và giảm độ lệch. Điều này đảm bảo tất cả các bộ phận của mạch đều nhận được tín hiệu xung nhịp với độ biến thiên thời gian tối thiểu.

Bù trễ

Sử dụng các phần tử trễ để bù cho sự chênh lệch độ dài đường dẫn. Kỹ thuật này giúp căn chỉnh thời gian đến của xung nhịp trên các phần khác nhau của FPGA.

Mục tiêu tối ưu hóa

Xác định các mục tiêu tối ưu hóa CTS phù hợp dựa trên yêu cầu thiết kế. Các mục tiêu này có thể bao gồm giảm thiểu độ lệch xung nhịp, giảm mức tiêu thụ điện năng hoặc đạt được biên độ thời gian cụ thể.

5. Kỹ thuật xung nhịp công suất thấp

Tiêu thụ điện năng là một mối quan tâm lớn trong FPGA tốc độ cao. Hãy xem xét các chiến lược xung nhịp tiêu thụ điện năng thấp sau:

Điều chỉnh điện áp và tần số động (DVFS)

Điều chỉnh tần số xung nhịp và điện áp cung cấp dựa trên khối lượng công việc để tiết kiệm điện năng trong thời gian hoạt động thấp. DVFS có thể tự động giảm tần số và điện áp, giảm mức tiêu thụ điện năng mà không ảnh hưởng đến hiệu suất.

Cổng đồng hồ

Triển khai hiệu quả cơ chế đóng xung nhịp (clock gating) để giảm công suất ở các mô-đun nhàn rỗi hoặc hoạt động thấp. Cơ chế đóng xung nhịp có thể được áp dụng ở nhiều cấp độ khác nhau của hệ thống phân cấp thiết kế để tối đa hóa khả năng tiết kiệm điện.

Miền đa điện áp

Tạo các miền điện áp khác nhau cho các khối mạch khác nhau để tối ưu hóa mức tiêu thụ điện năng. Phương pháp này cho phép các khối hiệu suất cao hoạt động ở điện áp cao hơn trong khi các khối công suất thấp hoạt động ở điện áp thấp hơn.

Những cân nhắc thực tế và phương pháp thiết kế

Việc triển khai các kỹ thuật đo thời gian tiên tiến đòi hỏi phải lập kế hoạch cẩn thận và phương pháp thiết kế mạnh mẽ. Dưới đây là những cân nhắc chính:

Mô phỏng và Xác minh

Mô phỏng và kiểm chứng kỹ lưỡng các vấn đề liên quan đến đồng hồ bằng các công cụ và phương pháp phù hợp. Mô phỏng giúp xác định các vấn đề tiềm ẩn ngay từ đầu quá trình thiết kế, cho phép điều chỉnh kịp thời.

Thiết kế để kiểm tra (DFT)

Kết hợp các điểm kiểm tra và cấu trúc liên quan đến xung nhịp để chẩn đoán lỗi hiệu quả. Các kỹ thuật DFT như chuỗi quét và tự kiểm tra tích hợp (BIST) có thể được sử dụng để kiểm tra mạng xung nhịp và đảm bảo độ tin cậy của chúng.

Thời gian đóng cửa

Đảm bảo đóng thời gian bằng cách phân tích cẩn thận thời gian thiết lập và giữ, độ chùng và các thông số thời gian khác. Đóng thời gian là điều cần thiết để đảm bảo thiết kế đáp ứng mọi ràng buộc về thời gian và hoạt động đáng tin cậy.

Quy trình thiết kế lặp lại

Tinh chỉnh các chiến lược xung nhịp thông qua nhiều lần lặp lại thiết kế và đo lường. Phương pháp lặp lại cho phép các nhà thiết kế tinh chỉnh mạng xung nhịp và đạt được hiệu suất tối ưu.

Kết luận

Việc nắm vững các kỹ thuật tạo xung nhịp tiên tiến là điều cần thiết để đạt được hiệu suất tối ưu trong các thiết kế FPGA tốc độ cao. Bằng cách cân nhắc kỹ lưỡng việc phân phối xung nhịp, thiết kế PLL, cổng xung nhịp, CTS và các chiến lược tiết kiệm năng lượng, các kỹ sư có thể cải thiện đáng kể hiệu suất hệ thống, giảm mức tiêu thụ điện năng và nâng cao độ tin cậy của thiết kế. Việc học hỏi liên tục và thích nghi với các công nghệ mới nổi là rất quan trọng để luôn dẫn đầu trong lĩnh vực phát triển nhanh chóng này.

Các kỹ thuật xung nhịp tiên tiến đóng vai trò thiết yếu trong việc mở rộng giới hạn hiệu năng của FPGA. Bằng cách hiểu và triển khai các chiến lược này, các kỹ sư có thể tạo ra những thiết kế không chỉ đáp ứng mà còn vượt xa những yêu cầu khắt khe của các ứng dụng tốc độ cao hiện đại. Hãy nắm bắt những thách thức và cơ hội mà xung nhịp tiên tiến mang lại để thúc đẩy sự đổi mới và xuất sắc trong các dự án FPGA của bạn.