Thiết kế để kiểm tra: Các số liệu về khả năng kiểm soát và khả năng quan sát

Khám phá cách các số liệu về khả năng kiểm soát và khả năng quan sát giúp việc kiểm tra mạch trở nên dễ dàng và hiệu quả.

Trong thử nghiệm kỹ thuật số, chỉ biết lỗi nào có thể tồn tại là chưa đủ. Chúng ta phải hiểu mức độ dễ dàng kích hoạt lỗi và khả năng ảnh hưởng của lỗi lan truyền đến điểm quan sát được . Đây là lúc các phép đo khả năng kiểm soát và khả năng quan sát phát huy tác dụng. Các phép đo này cung cấp nền tảng định lượng để đánh giá và cải thiện khả năng kiểm tra trong mạch logic tổ hợp và tuần tự.

Các số liệu này hướng dẫn các công cụ ATPG, chiến lược chèn điểm kiểm tra, thiết kế chuỗi quét và thậm chí ảnh hưởng đến các hướng dẫn mã hóa RTL cho các thiết kế thân thiện với thử nghiệm.

Tại sao chúng ta cần khả năng kiểm soát và khả năng quan sát?

Để một cuộc thử nghiệm có thể phát hiện ra lỗi, ba điều phải xảy ra:

- Lỗi phải được kích hoạt — nút lỗi phải có giá trị logic ngược lại với trạng thái bị kẹt của nó.

- Hiệu ứng lỗi phải được lan truyền — nó phải đi qua các cổng logic mà không bị che khuất.

- Hiệu ứng lỗi phải được quan sát — nó phải xuất hiện ở đầu ra chính hoặc flip-flop quét.

Khả năng kiểm soát và khả năng quan sát giúp chúng ta dự đoán mức độ khó khăn hay dễ dàng để đáp ứng từng điều kiện này. Khả năng kiểm soát kém có nghĩa là một số lỗi nhất định sẽ khó được kích hoạt; khả năng quan sát kém có nghĩa là ngay cả những lỗi đã được kích hoạt cũng có thể không được phát hiện.

Các loại số liệu

Để định lượng khả năng kiểm tra của tín hiệu, các chuyên gia dựa vào một số số liệu đã được thiết lập, bao gồm:

- SCOAP (CC0, CC1, CO): Các biện pháp cấu trúc về mức độ khó khăn khi đưa một nút về 0 hoặc 1 và mức độ khó khăn khi quan sát lỗi tại nút đó.

- COP (Tích số khả năng kiểm soát × khả năng quan sát): Điểm kết hợp làm nổi bật các nút cần chèn điểm kiểm tra nhất.

- Chênh lệch Boolean: Một số liệu chức năng ước tính xác suất sự thay đổi tại một nút sẽ ảnh hưởng đến nút khác.

- Số liệu khoảng cách: Đếm độ dài đường dẫn đơn giản hoặc khoảng cách có trọng số từ một nút đến đầu ra chính, được sử dụng như một phương pháp thay thế nhanh để quan sát.

1) Số liệu SCOAP

Để cải thiện khả năng kiểm thử của thiết kế một cách có hệ thống, chúng ta cần một phương pháp để đo lường mức độ dễ dàng thiết lập giá trị logic cho mỗi tín hiệu nội bộ (khả năng điều khiển) và mức độ dễ dàng quan sát lỗi tại tín hiệu đó ở đầu ra (khả năng quan sát). Các chỉ số SCOAP (Chương trình Phân tích Khả năng Kiểm soát/Khả năng Quan sát Sandia) cung cấp chính xác điều này: ba giá trị vô hướng, CC0, CC1 và CO, gán điểm "khó khăn" cho mỗi nút trong danh sách mạng cấp cổng.

CC0, CC1 và CO là gì?

- CC0(n)

Khả năng điều khiển của nút n đến logic 0. CC0 thấp có nghĩa là dễ dàng ép n về 0; CC0 cao có nghĩa là cần nhiều thao tác đầu vào hoặc mức logic sâu. - CC1(n)

Khả năng điều khiển của nút n theo logic * 1. Tương tự, CC1 thấp biểu thị nút có thể được đưa lên 1 với ít nỗ lực; CC1 cao biểu thị độ phức tạp. - CO(n)

Khả năng quan sát của nút n . Nó phản ánh mức độ khó khăn khi một thay đổi bất ngờ tại n (do lỗi) lan truyền qua logic tiếp theo đến đầu ra chính.

Mỗi số liệu được biểu thị dưới dạng số nguyên không âm “chi phí” và được tính bằng cách duyệt qua netlist:

Khả năng điều khiển tính toán (CC0 & CC1)

- Khởi tạo Đối

với mỗi nút đầu vào chính (PI):

— CC0 = 1

— CC1 = 1 - Duyệt thuận tôpô:

Truy cập các cổng theo thứ tự đầu vào-đầu ra . Đối với cổng G có đầu vào i₁, i₂ … iₖ và đầu ra o :

- Cổng AND

• CC0(o) = 1 + min(CC0(i₁), CC0(i₂), …, CC0(iₖ))

(chỉ cần một đầu vào là 0)

• CC1(o) = 1 + Σ CC1(iⱼ) với j=1..k

(tất cả đầu vào phải là 1) - Cổng OR

• CC0(o) = 1 + Σ CC0(iⱼ)

(tất cả các đầu vào phải bằng 0)

• CC1(o) = 1 + min(CC1(i₁), CC1(i₂), …) - NAND/NOR

Giống như AND/OR nhưng đổi vai trò CC0/CC1 vì đầu ra bị đảo ngược. - XOR/XNOR

• CC0(o) = 1 + Σ CC0(iⱼ)

• CC1(o) = 1 + Σ CC1(iⱼ)

(mọi đầu vào phải được kiểm soát) - Cổng phức hợp Phân

tích thành các phép toán cơ bản hoặc sử dụng các công thức cụ thể.

Khả năng quan sát tính toán (CO)

- Khởi tạo

Đối với mỗi nút đầu ra chính (PO):

— CO = 0 - Duyệt ngược:

Truy cập các cổng theo thứ tự đầu ra-đầu vào . Với mỗi cổng G có đầu ra o và đầu vào i₁…iₖ : - Đối với mỗi đầu vào iⱼ :

- Cổng AND

CO(iⱼ) = 1 + CO(o) + Σ CC1(iₘ), đối với mọi m ≠ j

(đầu vào phụ phải bằng 1 để truyền bá sự thay đổi) - Cổng OR

CO(iⱼ) = 1 + CO(o) + Σ CC0(iₘ), đối với mọi m ≠ j

(đầu vào bên phải bằng 0) - NAND/NOR

Tổng đầu vào cùng phía, vì phép đảo ngược không ảnh hưởng đến phép tính khả năng quan sát. - XOR/XNOR

CO(iⱼ) = 1 + CO(o) + Σ min(CC0(iₘ), CC1(iₘ)), với mọi m ≠ j

(mỗi đầu vào bên phải cho phép đầu ra phụ thuộc vào iⱼ)

Diễn giải các giá trị SCOAP

- CC0 hoặc CC1 thấp (ví dụ: 1–3) có nghĩa là nút dễ điều khiển theo giá trị logic đó.

- CC cao (ví dụ: >10) cho thấy việc buộc giá trị đó đòi hỏi logic sâu hoặc nhiều ràng buộc đầu vào.

- CO thấp (gần 0) cho biết bất kỳ nhiễu loạn nào tại nút đều dễ dàng xuất hiện ở đầu ra; CO cao (~10+) có nghĩa là nút bị ẩn sau logic cổng hoặc logic hội tụ, khiến cho việc quan sát các tác động lỗi trở nên khó khăn.

Ví dụ

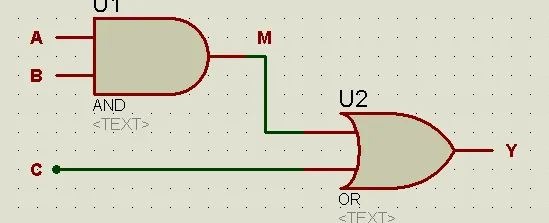

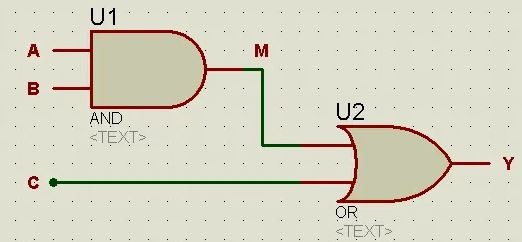

Hãy xem xét một logic nhỏ gồm 2 cấp độ:

- Các đầu vào chính A, B, C có CC0=CC1=1.

- Đối với cổng AND:

CC0(M) = 1 + min(1,1) = 2

CC1(M) = 1 + (1+1) = 3 - Đối với cổng OR:

CC0(Y) = 1 + (CC0(M) + CC0(C)) = 1 + (2 + 1) = 4

CC1(Y) = 1 + min(CC1(M), CC1(C)) = 1 + min(3,1) = 2 - Khả năng quan sát ngược:

CO(Y) = 0

Đối với M là đầu vào của OR: CO(M) = 1 + CO(Y) + CC0(C) = 1 + 0 + 1 = 2

Đối với C: CO(C) = 1 + 0 + CC0(M) = 1 + 2 = 3

Đối với A tại AND: CO(A) = 1 + CO(M) + CC1(B) = 1 + 2 + 1 = 4

(và tương tự đối với B)

Các giá trị này cung cấp thông tin chi tiết chính xác về nút nào có thể kiểm tra được và nút nào cần can thiệp DFT.

2) Khả năng kiểm soát-Khả năng quan sát (COP)

Tích số Kiểm soát-Khả năng Quan sát , hay COP , kết hợp độ khó của một nút để đạt được giá trị logic với độ khó của việc quan sát lỗi tại nút đó. Nó được định nghĩa đơn giản như sau:

COP(n) = min(CC0(n), CC1(n)) × CO(n)

- CC0(n) là chi phí để buộc nút n về logic 0

- CC1(n) là chi phí để buộc nút n về logic 1

- CO(n) là chi phí để truyền lỗi tại nút n đến đầu ra chính

- Chúng tôi sử dụng giá trị tối thiểu của CC0 và CC1 vì điều kiện kích hoạt dễ dàng hơn sẽ chi phối việc khởi tạo lỗi

Giá trị COP cao xác định điểm nóng có khả năng kiểm tra thực sự — các nút vừa khó kiểm soát vừa khó quan sát.

Cách tính CC0, CC1 và CO

Trước khi tính toán COP, bạn phải lấy số liệu SCOAP cho từng nút:

Khởi tạo chi phí I/O chính

- Đối với mỗi đầu vào chính, đặt CC0 = 1 và CC1 = 1

- Đối với mỗi đầu ra chính, đặt CO = 0

Tính toán CC0 và CC1 trong một lần chuyển tiếp

- Cổng chuyển tiếp từ đầu vào đến đầu ra

- Đối với cổng AND đầu ra Y với đầu vào A và B:

- CC0(Y) = 1 + phút(CC0(A), CC0(B))

- CC1(Y) = 1 + CC1(A) + CC1(B)

- Đối với đầu ra cổng OR Y:

- CC0(Y) = 1 + CC0(A) + CC0(B)

- CC1(Y) = 1 + phút(CC1(A), CC1(B))

- Áp dụng các công thức tương tự cho NAND, NOR, XOR, v.v., sử dụng phép đảo ngược và yêu cầu đầu vào phụ

Tính toán CO trong một lần chạy ngược

- Cổng chuyển tiếp từ đầu ra trở lại đầu vào

- Đối với đầu vào cổng AND A điều khiển Y, với đầu vào B còn lại:

- CO(A) = 1 + CO(Y) + CC1(B)

(B phải bằng 1 để sự thay đổi tại A có thể ảnh hưởng đến Y) - Đối với đầu vào cổng OR A: CO(A) = 1 + CO(Y) + CC0(B)

- Lặp lại cho tất cả các loại cổng, cộng chi phí khả năng điều khiển của các đầu vào phụ và thêm một cho chính cổng

Ví dụ về COP

Hãy xem xét một nút n mà chúng ta đã tìm thấy:

- CC0(n) = 8

- CC1(n) = 12

- CO(n) = 10

Đầu tiên, hãy lấy chi phí kiểm soát nhỏ hơn:

phút(CC0, CC1) = 8

Sau đó nhân với chi phí quan sát:

COP(n) = 8 × 10 = 80

COP 80 đánh dấu nút n là ứng cử viên chính cho việc chèn điểm kiểm tra hoặc tái cấu trúc logic, vì sẽ khó có thể bao phủ được bằng các mẫu kiểm tra hiện có.

3) Sự khác biệt Boolean

Trong khi các số liệu SCOAP cung cấp góc nhìn cấu trúc về khả năng kiểm soát và khả năng quan sát, thì chênh lệch Boolean lại cung cấp góc nhìn chức năng về cách một thay đổi tại một nút ảnh hưởng đến nút khác. Nó ước tính xác suất việc chuyển đổi một tín hiệu nội bộ cụ thể sẽ tạo ra thay đổi ở đầu ra chính, dựa trên các biểu thức Boolean của mạch.

Sự khác biệt của Boolean là gì?

Với hàm logic F(X₁, X₂, …, Xₙ) và một nút Xᵢ, hiệu số Boolean ∂F/∂Xᵢ được định nghĩa là:

• ∂F/∂Xᵢ = F(X₁,…, Xᵢ=0,…,Xₙ) ⊕ F(X₁,…, Xᵢ=1,…,Xₙ)

Nói cách khác, chúng ta đánh giá F với Xᵢ bị ép về 0 và một lần nữa với Xᵢ bị ép về 1; phép toán OR loại trừ của hai kết quả đó cho chúng ta biết liệu sự thay đổi tại Xᵢ có thể đảo ngược đầu ra hay không.

- Nếu ∂F/∂Xᵢ = 1 cho một phép gán đầu vào nhất định, thì việc chuyển đổi Xᵢ sẽ đảo ngược đầu ra.

- Nếu ∂F/∂Xᵢ = 0, thì đầu ra không nhạy cảm với những thay đổi trong Xᵢ theo phép gán đó.

Sự khác biệt Boolean như một ước tính khả năng quan sát

Bằng cách lấy trung bình ∂F/∂Xᵢ trên tất cả các phép gán đầu vào khả dĩ, chúng ta thu được xác suất Pᵢ mà một phép lật tại nút Xᵢ lan truyền đến đầu ra. Pᵢ cao có nghĩa là Xᵢ có thể quan sát được về mặt chức năng , trong khi Pᵢ thấp biểu thị sự che khuất hoặc không nhạy cảm.

Trong thực tế:

- Người ta có thể lấy mẫu một tập hợp con các vectơ đầu vào (ví dụ: các mẫu ATPG) và tính toán ∂F/∂Xᵢ cho từng vectơ.

- Tỷ lệ các vectơ có ∂F/∂Xᵢ = 1 so với tổng số vectơ lấy mẫu ước tính khả năng quan sát chức năng.

Tính toán sự khác biệt Boolean trong danh sách mạng cấp cổng

Ở cấp độ cổng, sự khác biệt Boolean có thể được tính toán đệ quy bằng cách sử dụng các quy tắc cục bộ:

- Cổng AND Y = A & B

∂Y/∂A = B

∂Y/∂B = A - Cổng OR Y = A | B

∂Y/∂A = ¬B

∂Y/∂B = ¬A - Cổng KHÔNG Y = ¬A

∂Y/∂A = 1 - Cổng XOR Y = A ⊕ B

∂Y/∂A = 1

∂Y/∂B = 1

Bằng cách truyền những khác biệt cục bộ này qua netlist đến mọi đầu ra chính và kết hợp (OR logic) trên nhiều đầu ra, chúng ta có được ∂F/∂Xᵢ tổng thể cho mỗi nút bên trong.

Ví dụ

Hãy xem xét một hàm logic nhỏ:

Y = (A VÀ B) HOẶC C

Tính ∂Y/∂A

- Sửa B=1, C=0:

Y(A=0) = (0 & 1) | 0 = 0

Y(A=1) = (1 & 1) | 0 = 1

∂Y/∂A = 1 ⊕ 0 = 1 - Sửa B=0, C=1:

Y(A=0) = (0 & 0) | 1 = 1

Y(A=1) = (1 & 0) | 1 = 1

∂Y/∂A = 1 ⊕ 1 = 0

Lấy mẫu trên cả bốn tổ hợp đầu vào sẽ cho ra hai trường hợp trong đó ∂Y/∂A = 1 và hai trường hợp trong đó ∂Y/∂A = 0, do đó P_A ước tính = 0,5. Do đó, nút A có 50% khả năng xảy ra lỗi chuyển đổi tại Y.

4) Số liệu khoảng cách

Ngoài các phép đo SCOAP cấu trúc và phép đo chênh lệch Boolean chức năng, phép đo khoảng cách cung cấp một phương pháp nhẹ nhàng để ước tính khoảng cách "xa" của một nút nội bộ so với các đầu ra quan sát được. Bằng cách đếm các mức logic hoặc cộng các trọng số cổng, phép đo khoảng cách đóng vai trò là một đại diện nhanh cho khả năng quan sát của một nút — các nút nằm sâu nhiều cấp thường khó lan truyền lỗi hơn, trong khi các nút chỉ cách một hoặc hai cổng thì dễ dàng hơn.

Đơn vị đo khoảng cách là gì?

Một phép đo khoảng cách gán cho mỗi nút một số nguyên không âm phản ánh độ dài đường dẫn ngắn nhất của nó đến bất kỳ đầu ra chính hoặc flip-flop quét-chụp nào. Các biến thể phổ biến bao gồm:

- Khoảng cách mức không

trọng số Đếm mỗi cổng hoặc chuyển tiếp ròng là “1”. Khoảng cách của nút n là số cổng tối thiểu giữa n và bất kỳ điểm quan sát nào. - Khoảng cách có trọng số:

Gán các trọng số khác nhau cho các cổng khác nhau (ví dụ: cổng phức tạp có trọng số cao hơn) hoặc thêm chi phí kiểm soát đầu vào phụ. Khoảng cách là tổng trọng số dọc theo đường dẫn ngắn nhất.

Cách tính khoảng cách

Khởi tạo Điểm quan sát

Đặt khoảng cách của mọi đầu ra chính (và mọi nút chụp quét-FF) thành 0 .

Duyệt ngược theo chiều rộng (Breadth-First)

Bắt đầu từ tất cả các điểm quan sát, duyệt ngược danh sách mạng qua các cạnh quạt. Với mỗi nút tiền nhiệm p:

- Khoảng cách không trọng số:

khoảng cách (p) = 1 + phút (khoảng cách của mỗi người kế nhiệm quạt ra) - Khoảng cách có trọng số:

distance(p) = gate_weight(G) + min(khoảng cách của mỗi người kế nhiệm)

Lặp lại cho đến khi tất cả các nút được chỉ định

Tiếp tục duyệt ngược cho đến khi mọi nút trong danh sách mạng đều có giá trị khoảng cách.

Tại sao số liệu khoảng cách lại quan trọng

- Ước tính khả năng quan sát nhanh

Các nút có khoảng cách = 1 hoặc 2 thường dễ quan sát; các nút có khoảng cách > 10 có thể yêu cầu các điểm kiểm tra đặc biệt hoặc nỗ lực ATPG tập trung. - Thuật toán ATPG

ATPG giai đoạn đầu có thể sử dụng khoảng cách để xếp hạng các đường truyền lan truyền — các nút có khoảng cách ngắn hơn sẽ được ưu tiên, giảm việc quay lại. - Lập kế hoạch DFT

Các nút khoảng cách xa đánh dấu các hình nón logic có thể được hưởng lợi từ việc chèn điểm quan sát , đặc biệt là khi chuỗi quét không thể tiếp cận trực tiếp chúng. - Hướng dẫn mã hóa RTL

Các nhà thiết kế có thể theo dõi khoảng cách trong quá trình tổng hợp để tránh tạo ra các hình nón logic quá sâu mà không có điểm bắt giữ trung gian.

Ví dụ

Hãy tưởng tượng một chuỗi logic ba cấp độ:

A → G1 → G2 → G3 → Y(đầu ra)

- Y có khoảng cách là 0

- Đầu ra của G3 (gọi là N3) có khoảng cách là 1

- Đầu ra của G2 (N2) có khoảng cách 2

- Đầu ra của G1 (N1) có khoảng cách 3

- Đầu vào chính A có khoảng cách 4

Lỗi trên N1 (khoảng cách 3) phải lan truyền qua ba cổng để đến Y, cho thấy cần nỗ lực cao hơn lỗi trên N3 (khoảng cách 1).

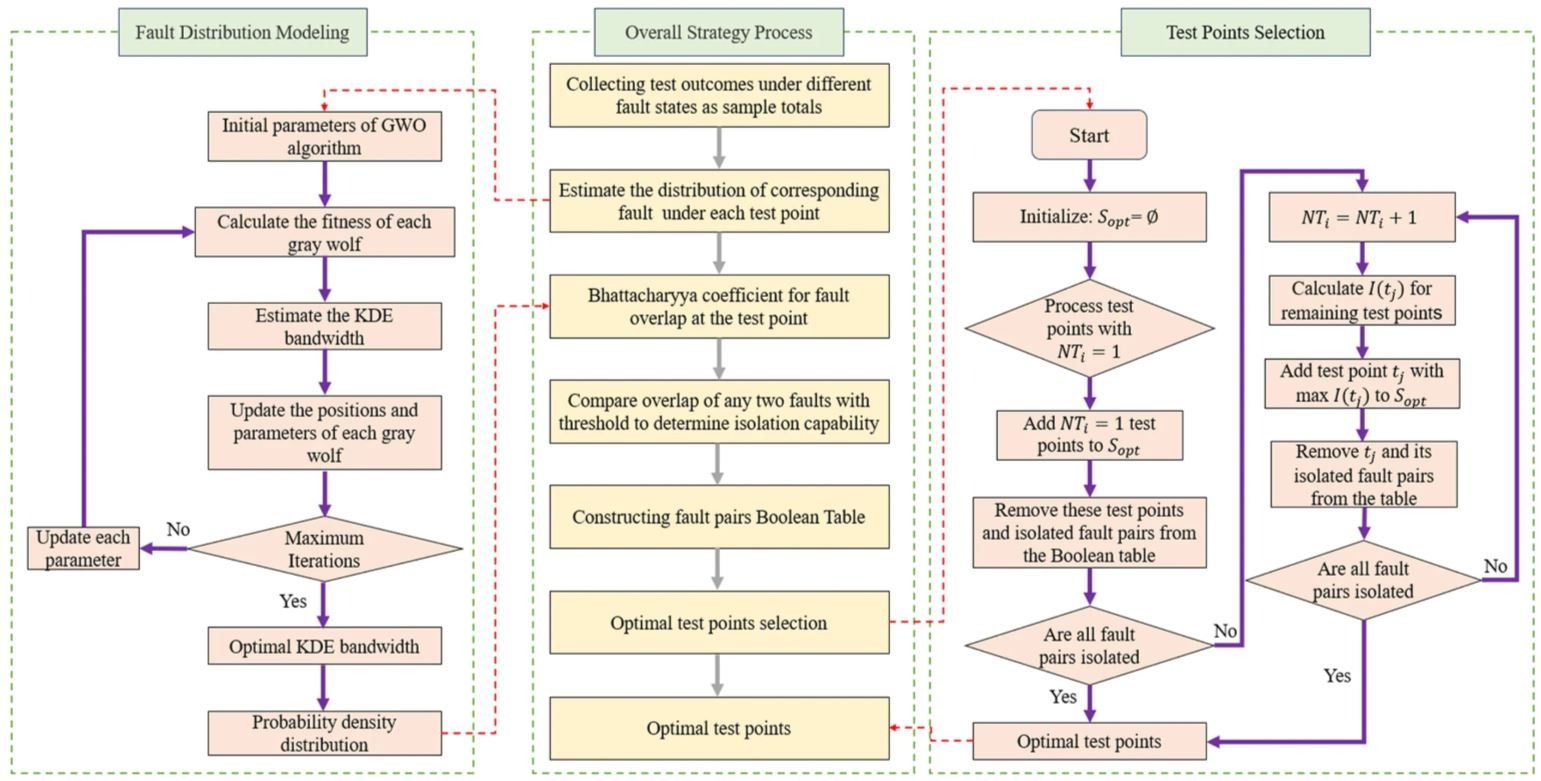

Áp dụng các chỉ số khả năng kiểm tra trong DFT

Thiết kế cho Khả năng Kiểm thử dựa trên các số liệu định lượng để xác định chính xác vị trí lỗi khó phát hiện nhất và vị trí cải tiến mục tiêu sẽ mang lại lợi ích lớn nhất. Bằng cách hợp nhất các phép đo SCOAP , sai phân Boolean và khoảng cách , các kỹ sư có được cái nhìn toàn diện về khả năng kiểm thử, từ đó hỗ trợ ATPG, chèn điểm kiểm thử và tối ưu hóa thiết kế.

1. Hướng dẫn ATPG và ưu tiên mẫu

Các công cụ ATPG sử dụng khả năng điều khiển SCOAP (CC0, CC1) để quyết định lỗi nào cần nhắm mục tiêu trước — lỗi trên các nút dễ điều khiển thường có thể được kích hoạt nhanh chóng, trong khi lỗi có giá trị CC cao có thể cần xử lý đặc biệt. Khả năng quan sát SCOAP (CO) giúp lựa chọn đường truyền để tối đa hóa khả năng lỗi đến được đầu ra. Bằng cách kết hợp những yếu tố này vào COP , ATPG có thể xếp hạng lỗi theo độ khó kiểm tra và phân bổ nỗ lực tìm kiếm vào những nơi quan trọng nhất.

Chênh lệch Boolean giúp tinh chỉnh quy trình này hơn nữa. Các nút có xác suất chênh lệch Boolean cao có độ nhạy về mặt chức năng, nghĩa là các nút chuyển đổi tại các điểm đó hầu như luôn ảnh hưởng đến đầu ra theo phân phối đầu vào thực tế. Lỗi trên các nút có chênh lệch Boolean thấp có thể bị trì hoãn hoặc chịu các mẫu "nhạy cảm" chuyên dụng. Các phép đo khoảng cách — đo độ dài đường dẫn ở cấp cổng đến đầu ra — hướng dẫn ATPG đến các tuyến đường ngắn hơn, ít bị che khuất hơn, giảm việc quay lui và cải thiện hiệu quả của mẫu.

2. Cải tiến Chèn điểm kiểm tra và DFT

Khi giá trị COP cao, điểm chênh lệch Boolean thấp hoặc giá trị khoảng cách lớn đánh dấu một nút là nút thắt cổ chai khả năng kiểm thử, các nhà thiết kế có thể chèn các điểm kiểm soát (để cải thiện khả năng kiểm soát) hoặc các điểm quan sát (để cải thiện khả năng quan sát). Ví dụ:

- Một nút có CC1 = 15, CC0 = 12 và CO = 20 (COP = 12 × 20 = 240) rõ ràng sẽ được hưởng lợi từ điểm kiểm soát làm giảm CC.

- Một nút có xác suất chênh lệch Boolean dưới 10% cho thấy nút đó cần một điểm quan sát cấu trúc hoặc một mẫu chuyên biệt.

- Một nút có khoảng cách = 8 có thể không thể tiếp cận được chỉ bằng chuỗi quét và do đó cần có chốt bắt giữ trung gian.

Bằng cách tính toán lại cả ba số liệu sau mỗi lần thay đổi DFT, các kỹ sư có thể xác nhận rằng mỗi lần chèn điểm kiểm tra hoặc tái cấu trúc logic đều mang lại những cải tiến có thể đo lường được.

3. Phản hồi và hình dung thiết kế ban đầu

Trong giai đoạn RTL và cấp cổng, việc chạy phân tích khả năng kiểm thử kết hợp sẽ làm nổi bật các "vùng tối" trong thiết kế — các cụm nút có điểm kém trên tất cả các chỉ số. Các công cụ trực quan hóa có thể mã hóa màu các hình nón logic theo COP, xác suất chênh lệch Boolean hoặc khoảng cách, giúp dễ dàng phát hiện các quạt hội tụ lại, logic lồng nhau sâu hoặc các cấu trúc cổng đòi hỏi nỗ lực ATPG lớn.

Được trang bị những hiểu biết sâu sắc này, các kiến trúc sư có thể cấu trúc lại các khối quan trọng — làm phẳng logic, cân bằng quạt hoặc điều chỉnh cổng xung nhịp — để tạo ra các thiết kế có thể kiểm tra được nhiều hơn từ lâu trước khi có silicon.

4. Vòng lặp đóng liên tục

Cuối cùng, các số liệu kiểm tra này sẽ đưa vào vòng lặp DFT lặp lại :

- Phân tích netlist với SCOAP, sự khác biệt Boolean và khoảng cách

- Xác định các nút ưu tiên cao để tập trung ATPG hoặc chèn DFT

- Cải thiện thiết kế bằng chuỗi quét, điểm kiểm tra hoặc tái cấu trúc logic

- Tạo mẫu thử nghiệm và chạy mô phỏng lỗi

- Đo lường phạm vi phủ sóng và xem xét lại các số liệu cho các điểm nghẽn còn lại