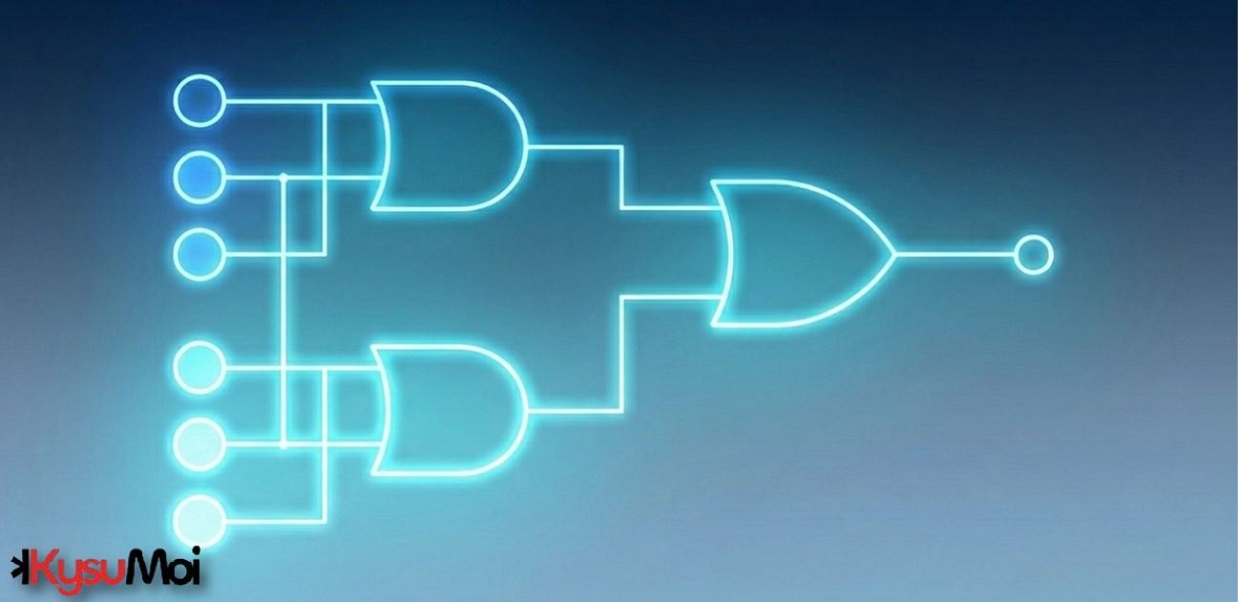

Triển khai hai cấp độ của cổng logic

Mở khóa tốc độ thiết kế kỹ thuật số bằng cách thành thạo nghệ thuật triển khai cổng logic hai cấp!

Thuật ngữ "logic hai cấp" đề cập đến một thiết kế logic sử dụng không quá hai cổng logic giữa đầu vào và đầu ra. Điều này không có nghĩa là toàn bộ thiết kế sẽ chỉ có hai cổng logic, nhưng nó có nghĩa là đường dẫn duy nhất từ đầu vào đến đầu ra sẽ chỉ có hai cổng logic.

Trong logic hai cấp, bất kể tổng số cổng logic, số lượng cổng logic tối đa có thể được xếp tầng giữa bất kỳ đầu vào và đầu ra nào là hai. Đầu ra của cổng logic cấp một được kết nối với đầu vào của cổng logic cấp hai trong cấu hình này.

Logic Gate là gì?

Cổng logic là một thành phần cơ bản của mạch kỹ thuật số thực hiện các phép toán logic cơ bản. Cũng giống như cấu trúc đại số hoặc hệ thống toán học, chúng thực hiện các phép toán logic cơ bản rất quan trọng trong việc thiết kế các mạng kỹ thuật số phức tạp. Một cổng có thể hoạt động áp dụng đại số Boolean với đầu vào có thể được cung cấp cho nó và mang lại kết quả đầu ra. Dưới đây là tổng quan nhanh về các cổng logic chính được sử dụng trong thiết kế logic hai cấp:

- Cổng AND: Chỉ xuất ra true (1) nếu tất cả các đầu vào đều đúng.

- Cổng HOẶC: Xuất ra đúng (1) nếu ít nhất một đầu vào là đúng.

- Cổng NAND: Đầu ra true (1) trừ khi tất cả các đầu vào đều đúng.

- Cổng NOR: Chỉ xuất ra true (1) nếu tất cả các đầu vào đều sai.

Ví dụ về triển khai logic hai cấp

Chúng tôi khám phá bốn cổng logic trong triển khai logic hai cấp: AND Gate, OR Gate, NAND Gate và NOR Gate. Có tổng cộng 16 tổ hợp logic hai cấp độ nếu chúng ta chọn một trong bốn cổng này ở cấp độ đầu tiên và một cổng ở cấp độ thứ hai. Đây là

VÀ-VÀ, VÀ-HOẶC, VÀ-NAND, VÀ-KHÔNG,

HOẶC-VÀ, HOẶC-HOẶC, HOẶC-NAND, HOẶC-KHÔNG,

NAND-AND, NAND-OR, NAND-NAND, NAND-NOR,

NOR-AND, NOR-HOẶC, NOR-NAND, NOR-NOR.

Mỗi tổ hợp hai cấp độ thực hiện một hàm logic riêng biệt. 16 sự kết hợp này được chia thành hai loại.

- Dạng thoái hóa của kết hợp cổng logic

- Dạng không thoái hóa của kết hợp cổng logic

Dạng thoái hóa

Dạng thoái hóa xảy ra khi đầu ra của việc nhận thức logic hai cấp có thể đạt được chỉ với một cổng logic. Ưu điểm của dạng thoái hóa là số lượng đầu vào của cổng Logic đơn tăng lên, dẫn đến sự gia tăng fan-in của các cổng logic.

Trong 16 sự kết hợp đó, có 8 dạng thoái hóa. Dưới đây là các trường hợp của từng loại thoái hóa này.

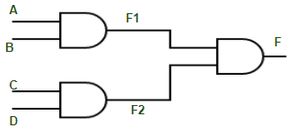

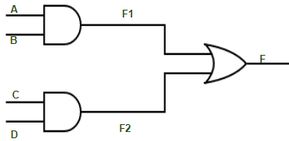

Triển khai AND-AND

Bởi vì toàn bộ hàm dẫn đến hàm AND của tất cả các đầu vào, tổ hợp cổng AND-AND này là một dạng thoái hóa.

Đầu ra của cổng logic cấp một: F1 = AB và F2 = CD. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = F1F2, có nghĩa là F = ABCD.

Triển khai OR-OR

Đầu ra của tổ hợp cổng OR-OR là Hàm logic OR. Với sự kết hợp này, hàm OR có thể được thực hiện với một số đầu vào.

Đầu ra của cổng logic cấp một: F1 = A + B và F2 = C + D. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = F1 + F2 có nghĩa là F = A + B + C + D.

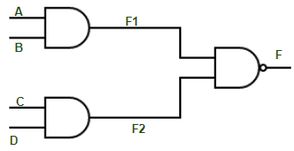

Triển khai AND-NAND

Cổng AND có mặt ở cấp độ đầu tiên của quá trình triển khai logic này, trong khi cổng NAND có mặt ở cấp độ thứ hai. Một ví dụ về thực hiện logic AND-NAND được hiển thị trong sơ đồ bên dưới.

Đầu ra của cổng logic cấp một: F1 = AB và F2 = CD. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1F2) 'có nghĩa là F = (ABCD)'.

Triển khai OR-NOR

Sự kết hợp của các cổng OR-NOR dẫn đến chức năng logic NOR. Và dạng thoái hóa này có thể được sử dụng cho hàm NOR với nhiều đầu vào.

Đầu ra của cổng logic cấp một: F1 = A + B và F2 = C + D. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1 + F2) 'có nghĩa là F = (A + B + C + D)'.

Triển khai NAND-NOR

Hàm kết quả của NAND-NOR trong logic hai cấp là logic AND. Sau đây là biểu hiện và sơ đồ của nó:

Đầu ra của cổng logic cấp đầu tiên: F1 = (AB) ' và F2 = (CD) '. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1 + F2) 'có nghĩa là F = ((AB) '+ (CD) ')'.

Triển khai NOR-NAND

Bởi vì tổ hợp NOR-NAND cũng tạo ra một hàm OR, nó cũng là một dạng thoái hóa. Sau đây là một ví dụ về nó với một sơ đồ;

Đầu ra của cổng logic cấp đầu tiên: F1 = (A + B) ' và F2 = (C + D)'. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1. F2)' có nghĩa là F = ((A + B) '(C + D) ')'.

Triển khai NAND-OR

Sự kết hợp này, giống như sự kết hợp AND-NAND, tạo ra một hàm logic NAND.

Đầu ra của cổng logic cấp đầu tiên: F1 = (AB) ' và F2 = (CD) '. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1 + F2) có nghĩa là F = ((AB) '+ (CD) ') = (ABCD) '.

Triển khai NOR-AND

Sự kết hợp này giống với sự kết hợp OR-NOR vì sự kết hợp này cũng dẫn đến hàm NOR.

Đầu ra của cổng logic cấp đầu tiên: F1 = (A + B) ' và F2 = (C + D)'. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1. F2) có nghĩa là F = (((A + B) '(C + D) ') = (A + B + C + D)'.

Dạng không thoái hóa

Một dạng không thoái hóa xảy ra khi không thể đạt được đầu ra của nhận thức logic hai cấp bằng cách sử dụng một cổng logic duy nhất. Các dạng không thoái hóa là các tổ hợp logic hai cấp thực hiện dạng Tổng sản phẩm hoặc dạng Sản phẩm của Tổng.

Trong 16 sự kết hợp đó, có 8 dạng không thoái hóa. Dưới đây là các trường hợp của từng loại không thoái hóa này.

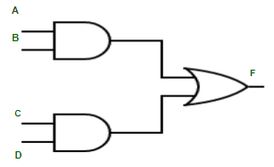

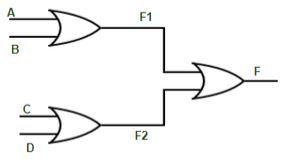

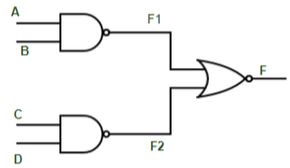

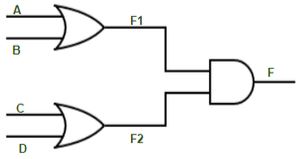

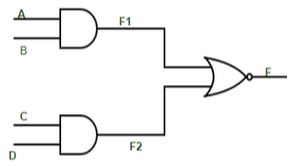

Triển khai AND-OR

Cổng cấp đầu tiên trong tổ hợp While-OR là cổng AND và cổng cấp thứ hai là cổng OR. Như thể hiện trong sơ đồ bên dưới, sự kết hợp này thực hiện biểu mẫu Tổng sản phẩm (SOP).

Đầu ra của cổng logic cấp một: F1 = AB và F2 = CD. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1 + F2) có nghĩa là F = (AB + CD).

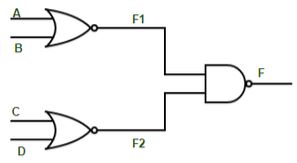

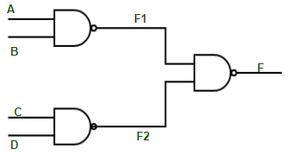

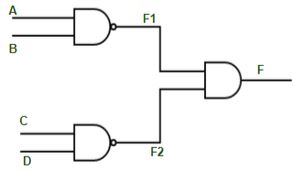

Triển khai NAND-NAND

NAND là một cổng phổ quát và sự kết hợp NAND-NAND của nó, giống như tổ hợp AND-OR, được sử dụng để tạo ra dạng Tổng sản phẩm.

Đầu ra của cổng logic cấp một: F1 = (AB) ' và F2 = (CD) '. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1. F2)' có nghĩa là F = (AB) + (CD).

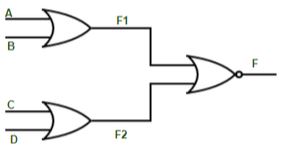

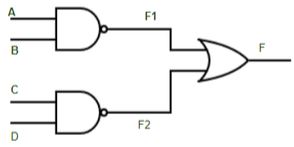

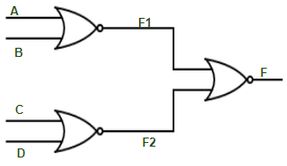

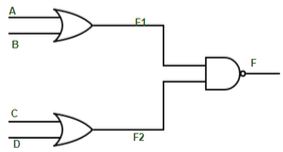

Thực hiện OR-AND

Cổng cấp đầu tiên trong tổ hợp OR-AND là cổng OR và cổng cấp thứ hai là cổng AND. Mẫu Tích của Tổng được thực hiện với tổ hợp OR-AND.

Đầu ra của cổng logic cấp một: F1 = (A + B) và F2 = (C + D). Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1. F2) có nghĩa là F = (A + B) (C + D).

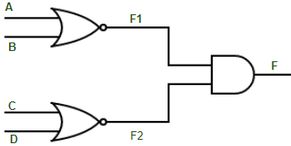

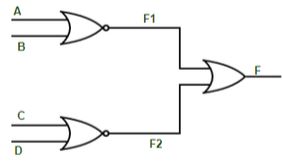

Triển khai NOR-NOR

NOR cũng là một cổng phổ quát và sự kết hợp NOR-NOR của nó có thể được sử dụng để thực hiện dạng Tích của Tổng.

Đầu ra của cổng logic cấp một: F1 = (A + B) ' và F2 = (C + D)'. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1 + F2) ' có nghĩa là F = ((A + B) '+ (C + D) ') '= (A + B) (C + D).

Triển khai AND-NOR

Sự kết hợp AND-NOR được sử dụng để thực hiện logic phức hợp AND-OR-INVERT (AOI).

Đầu ra của cổng logic cấp một: F1 = (AB) và F2 = (CD). Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1 + F2) 'có nghĩa là F = (AB + CD)'.

Triển khai NAND-AND

Biểu mẫu AND-OR-INVERT (AOI) cũng có thể được thực hiện bằng cách sử dụng NAND-AND.

Đầu ra của cổng logic cấp một: F1 = (AB) ' và F2 = (CD) '. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1F2) có nghĩa là F = (AB) '(CD) '= (AB + CD)'.

Triển khai OR-NAND

Biểu mẫu OR-NAND được sử dụng để thực hiện logic phức hợp OR-AND-INVERT (OAI).

Đầu ra của cổng logic cấp một: F1 = (A + B) và F2 = (C + D). Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1F2) 'có nghĩa là F = [(A + B) (C + D)]'.

Triển khai NOR-OR

Sự kết hợp NOR-OR, giống như sự kết hợp OR-NAND, được sử dụng để xây dựng logic phức hợp OR-AND-INVERT (OAI).

Đầu ra của cổng logic cấp một: F1 = (A + B) ' và F2 = (C + D)'. Các đầu ra này được áp dụng làm đầu vào của mức thứ hai, vì vậy đầu ra của mức thứ hai là F = (F1 + F2), có nghĩa là F = (A + B) '+ (C + D) '= [(A + B) (C + D)]'.

Ưu điểm của logic hai cấp độ

- Thiết kế đơn giản: Logic hai cấp độ làm giảm độ phức tạp của thiết kế vì tất cả những gì được sử dụng trong quy trình là các cổng logic chỉ sâu hai cấp độ. Điều này có thể giúp thiết kế mạch trở nên khả thi hơn và ít phức tạp hơn.

- Thực hiện hiệu quả: Chỉ có hai cấp độ cổng trong đó logic hai cấp độ có ý nghĩa hơn về tốc độ vì tín hiệu sẽ chỉ đi qua nhiều nhất một vài cổng.

- Giảm số lượng cổng: Nó có thể hữu ích trong thiết kế cấp một để giảm tổng số cổng, có thể giảm chi phí và mức tiêu thụ điện năng của thiết kế ưa thích từ cấp độ thứ hai.

Nhược điểm của logic hai cấp độ

- Độ phức tạp hạn chế: Giới hạn ở hai cấp độ có nghĩa là các chức năng logic có thể được thực hiện thuộc loại hạn chế hơn nhiều và điều này có thể không phù hợp với các ứng dụng nâng cao hoặc chuyên biệt hơn.

- Hạn chế thiết kế: Nếu một hệ thống được thiết kế chỉ với hai cấp độ cổng, cũng có thể để có được các chức năng mong muốn, cần phải có logic phức tạp hơn và do đó các thiết kế không dễ dàng lắm.

- Tiềm năng tăng cường sử dụng cổng: Có những tình huống điển hình, trong đó việc sử dụng logic hai cấp với chức năng yêu cầu có thể làm tăng số lượng cổng so với các trường hợp có thể sử dụng giải pháp đa cấp.

Kết luận

Logic hai cấp chứng tỏ hiệu quả trong việc tổ chức các phác thảo bên ngoài của dự án vì nó đặt ra giới hạn về số lượng mức cổng logic giữa đầu vào và đầu ra. Mặc dù điều này có thể giúp giảm tổng số lớp cần thiết trong thiết kế và có thể góp phần tăng hiệu quả của một số ứng dụng. Tuy nhiên, giới hạn hai cấp độ triển khai như vậy có thể không tốt cho tất cả các loại hàm logic, đặc biệt là đối với những loại cần các mạch phức tạp hơn. Việc nhận ra lợi ích và hạn chế của logic hai cấp độ là khá quan trọng để sử dụng nó vào thiết kế phù hợp của các mạch kỹ thuật số.