Bộ cộng Ripple Carry (RCA)

Hãy cùng tìm hiểu về Ripple Carry Adder

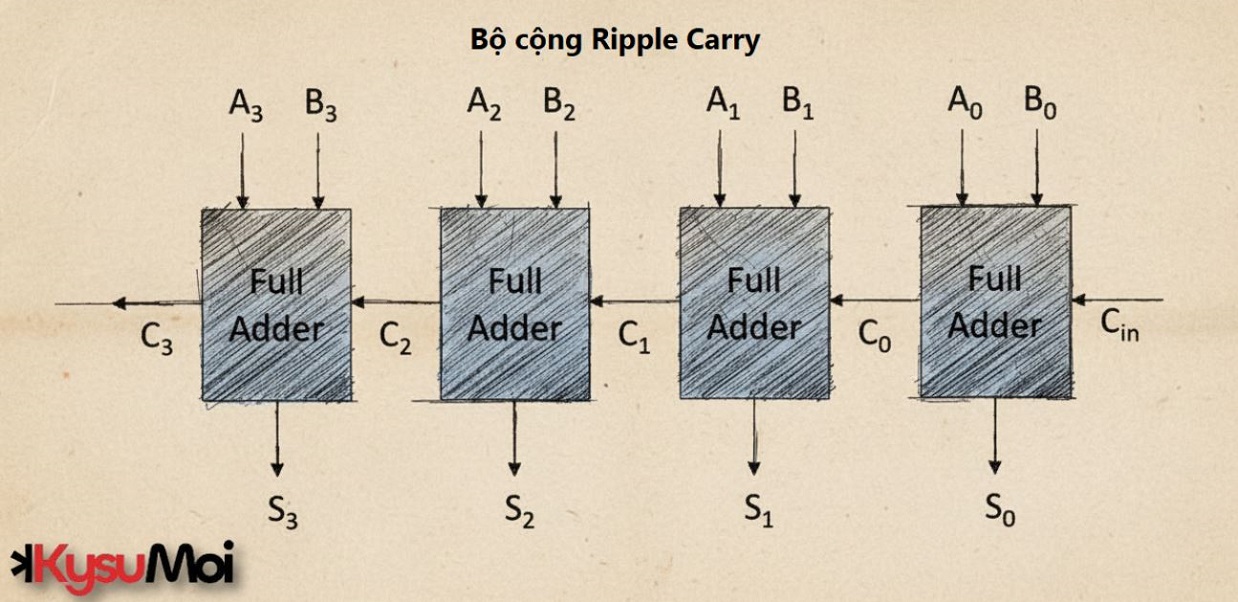

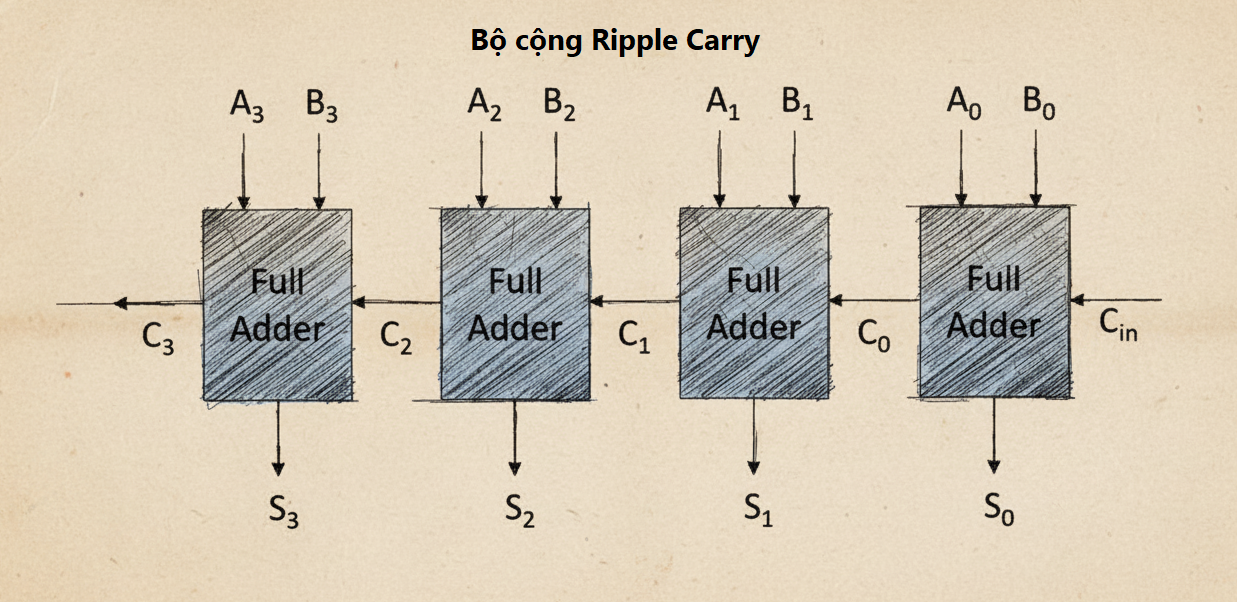

Như đã thảo luận, bộ cộng đầy đủ có thể thêm một bit vào hai đầu vào và thêm một bit nhớ được tạo ra từ giai đoạn trước. Để thêm nhiều chuỗi nhị phân 'n' bit, có thể sử dụng nhiều bộ cộng đầy đủ xếp tầng, tạo ra một bit nhớ và được áp dụng cho bộ cộng đầy đủ giai đoạn tiếp theo làm đầu vào cho đến giai đoạn cuối cùng của bộ cộng đầy đủ. Điều này xuất hiện dưới dạng gợn sóng bit nhớ đến giai đoạn tiếp theo, do đó nó được gọi là "Bộ cộng đầy đủ gợn sóng".

Tính toán độ trễ của bộ cộng mang gợn sóng

Độ trễ trường hợp xấu nhất = [(n-1) bộ cộng đầy đủ * độ trễ lan truyền mang của mỗi bộ cộng] + tổng độ trễ lan truyền của mỗi bộ cộng đầy đủ

Sơ đồ khối

Nhược điểm của Ripple Carry Adder

Một bit nhớ sẽ chuyển sang giai đoạn tiếp theo, trong khi tất cả các giai đoạn của bộ cộng đầy đủ không được sử dụng đồng thời. Mỗi giai đoạn của bộ cộng đầy đủ cần được tạo ra trước khi có thể cộng hai số của giai đoạn tiếp theo, do đó gây ra độ trễ lan truyền trong tính toán. Đây là lý do tại sao bộ cộng gợn sóng nhớ chậm hơn.

Vấn đề này được giải quyết bằng ' Carry Look Ahead Adder '.

Ưu điểm của Ripple Carry Adder

Do bố cục đơn giản và thiết kế ít phức tạp nên thời gian thiết kế nhanh hơn.

Mã Verilog của Ripple Carry Adder

module full_adder(

input a, b, cin,

output sum, cout

);

assign {sum, cout} = {a^b^cin, ((a & b) | (b & cin) | (a & cin))};

//or

//assign sum = a^b^cin;

//assign cout = (a & b) | (b & cin) | (a & cin);

endmodule

module ripple_carry_adder #(parameter SIZE = 4) (

input [SIZE-1:0] A, B,

input Cin,

output [SIZE-1:0] S, Cout);

genvar g;

full_adder fa0(A[0], B[0], Cin, S[0], Cout[0]);

generate // This will instantiate full_adder SIZE-1 times

for(g = 1; g<SIZE; g++) begin

full_adder fa(A[g], B[g], Cout[g-1], S[g], Cout[g]);

end

endgenerate

endmoduleMã Testbench

module RCA_TB;

wire [3:0] S, Cout;

reg [3:0] A, B;

reg Cin;

wire[4:0] add;

ripple_carry_adder rca(A, B, Cin, S, Cout);

assign add = {Cout[3], S};

initial begin

$monitor("A = %b: B = %b, Cin = %b --> S = %b, Cout[3] = %b, Addition = %0d", A, B, Cin, S, Cout[3], add);

A = 1; B = 0; Cin = 0; #3;

A = 2; B = 4; Cin = 1; #3;

A = 4'hb; B = 4'h6; Cin = 0; #3;

A = 5; B = 3; Cin = 1; #3;

$finish;

end

initial begin

$dumpfile("waves.vcd");

$dumpvars;

end

endmoduleĐầu ra:

A = 0001: B = 0000, Cin = 0 --> S = 0001, Cout[3] = 0, Addition = 1

A = 0010: B = 0100, Cin = 1 --> S = 0111, Cout[3] = 0, Addition = 7

A = 1011: B = 0110, Cin = 0 --> S = 0001, Cout[3] = 1, Addition = 17

A = 0101: B = 0011, Cin = 1 --> S = 1001, Cout[3] = 0, Addition = 9